# Design and Evaluation of a RISC Processor with a Tomasulo Scheduler

## Diplomarbeit

Lehrstuhl für Rechnerarchitektur Prof. Wolfgang J. Paul FB14 Informatik Universität des Saarlandes

Daniel Kröning

Januar 1999

Hiermit erkläre ich an Eides statt, daß ich für die Anfertigung dieser Arbeit keine anderen als die angegebenen Quellen verwendet habe. Ich versichere, die Arbeit noch keinem anderen Prüfungsamt vorgelegt zu haben.

Saarbrücken, im Januar 1999

Daniel Kröning

## **Contents**

| 1 | Intro | oduction                                | 1  |

|---|-------|-----------------------------------------|----|

|   | 1.1   | Results                                 | 1  |

|   | 1.2   | Outline                                 | 2  |

| 2 | The   | Scheduling Algorithm                    | 3  |

|   | 2.1   | The DLX Architecture                    | 3  |

|   | 2.2   | The Tomasulo Scheduling Algorithm       | 3  |

|   | 2.3   | The Reorder Buffer                      | 9  |

|   | 2.4   | The Overall Scheduling Protocol         | 9  |

|   | 2.5   | Overall Scheduling Example              | 12 |

| 3 | Tom   | asulo Hardware                          | 15 |

|   | 3.1   | Overview                                | 15 |

|   | 3.2   | The PC Environment                      | 18 |

|   | 3.3   | Instruction Memory Environment          | 19 |

|   | 3.4   | Instruction Register Environment        | 19 |

|   | 3.5   | Decode/Issue Environment                | 21 |

|   | 3.6   | The Reservation Station Environments    | 34 |

|   | 3.7   | Function Unit Environments              | 47 |

|   | 3.8   | CDB Control Environment                 | 49 |

|   | 3.9   | Reorder Buffer Environment              | 52 |

|   | 3.10  | Register File Environment               | 59 |

| 4 | Men   | nory System                             | 69 |

|   | 4.1   | Overview of the Data Memory System      | 69 |

|   | 4.2   | The Data Memory Reservation Station     | 71 |

|   | 4.3   | Dispatch Protocol                       | 71 |

|   | 4.4   | Implementation of the Dispatch Protocol | 73 |

|   | 4.5   | Memory Interface                        | 75 |

vi CONTENTS

| 5 | Cost | and Cycle Time                        | 81  |

|---|------|---------------------------------------|-----|

|   | 5.1  | Hardware Cost                         | 81  |

|   | 5.2  | Cycle Time                            | 85  |

|   | 5.3  | Quality Survey and Comparison         | 87  |

| 6 | Cor  | rectness                              | 89  |

|   | 6.1  | Data Consistency                      | 89  |

|   | 6.2  | Termination                           | 92  |

| 7 | Pers | pective                               | 95  |

| A | Aux  | iliary circuits                       | 97  |

|   | A.1  | The Find First One Circuit            | 97  |

|   | A.2  | Conditional Sign Extension            | 99  |

|   | A.3  | The Integer Function Unit             | 99  |

|   | A.4  | ROB Auxiliary Circuits                | 99  |

|   | A.5  | Calculation of EPC/EPCn               | 100 |

| В | The  | Cost and Delay Calculation Programs   | 103 |

|   | B.1  | The Hardware Cost Calculation Program | 103 |

|   | B.2  | The Delay Calculation Program         | 104 |

| C | The  | DLX Instruction Set                   | 107 |

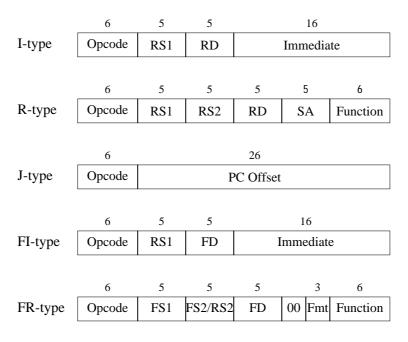

|   | C.1  | Instruction Formats                   | 107 |

|   | C.2  | Instruction Set Coding                | 108 |

## **Chapter 1**

## Introduction

The performance of today's microprocessors is astonishing. Beneath the progress in wafer technology, a big contribution to the improvements achieved in the past years was made by developing sophisticated scheduling algorithms. One of the major scheduling algorithms used in recent CPUs was specified long ago in 1967 by *Robert M. Tomasulo* [Tom67]. However, up to now concrete data on the impact of the algorithm on hardware cost and cycle time has been missing.

Thus, this thesis gives a detailed implementation of the Tomasulo scheduling algorithm for the DLX RISC architecture [HP96]. The design is based on a machine presented in [Lei98] and realizes full support for precise interrupts with a *reorder buffer* [SP88]. Cost and cycle time are calculated and evaluated with a formal model presented in [MP95]. The results are compared to other DLX implementations.

### 1.1 Results

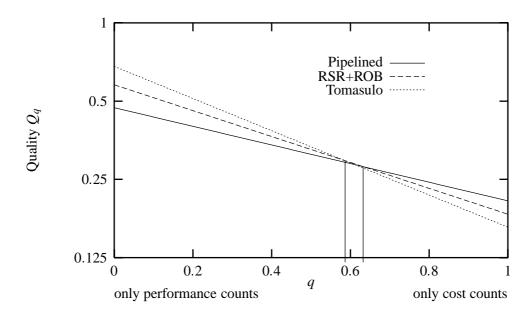

The Tomasulo scheduling algorithm is one of the most competitive scheduling algorithms. It provides low CPI rates down to 1.1 which is shown by simulations on common benchmarks in [Ger98, Del98]. This thesis shows that adding a Tomasulo scheduler does not have any impact on the cycle time of the CPU design.

The Tomasulo scheduling algorithm with precise interrupts is known to be expensive regarding hardware cost. A complete CPU core design counts about 236,000 gate equivalents, which is about two times as much as is needed by a pipelined design with equal function units. Compared to the total costs of a CPU design (including the first level cache), this is just an increase of 26 percent at a 44 percent higher performance.

## 1.2 Outline

Chapter 2 describes some basic concepts, like the hardware model and gives a rough overview of the design. It also includes a terse introduction to the Tomasulo scheduling algorithm itself. Chapter 3 presents all the implementation details on gate level other than the memory system, which is presented separately in chapter 4. In chapter 5, the analysis of the cost and cycle time of the design is carried out. The results are compared to other DLX implementations in order to evaluate the overall design quality impact of different scheduling algorithms. Chapter 6 contains the correctness proof for the hardware.

## **Chapter 2**

## The Scheduling Algorithm

## 2.1 The DLX Architecture

The underlying CPU is an implementation of the DLX architecture citeHP96. That is a load/store architecture with support for integer and floating point instructions. It has three register files:

- The **general purpose register file** (GPR) consists of  $32 \times 32$  integer registers ( $R_0,...,R_{31}$ ), where  $R_0$  is defined to be always zero. The general purpose registers are used for all integer operations and memory addressing purposes.

- The **floating point register file** (FPR) consists of 32 × 32 single precision floating point registers (FGR<sub>0</sub>,...,FGR<sub>31</sub>). These registers can also be accessed as 16 × 64 double precision floating point registers (FPR<sub>0</sub>, FPR<sub>2</sub>,...,FPR<sub>30</sub>), well aligned accesses assumed. FPR<sub>0</sub> is mapped onto FGR<sub>0</sub> and FGR<sub>1</sub>, and so on. The floating point registers are only used by FPU (floating point unit) instructions

- The **special purpose register file** (SPR) consists of several registers needed for special purposes such as flags and masks. An example is the IEEE floating point flags register.

The DLX instruction set (appendix C) is a RISC instruction set and is similar to SUN's MIPS instruction set.

## 2.2 The Tomasulo Scheduling Algorithm

The following sections give a short summary of the Tomasulo scheduling algorithm. The algorithm was specified in 1967 by Robert M. Tomasulo for an IBM 360/91 [Tom67]. A more comprehensive description is also available in [Mül97a].

In its original form, the Tomasulo scheduling algorithm is limited to two-address-instructions (one source, one destination, e.g., R1+=R2) and multiple sequential function units for each kind of operation. However, it is easy to extend the algorithm to handle today's common instructions with three addresses (two source registers, one destination, e.g., R1:=R2+R3). The algorithm is widely used, e.g., by IBM PowerPC, Intel Pentium-Pro or AMD K5 [Mot97, CS95].

### 2.2.1 Pipelining vs. Out-of-Order Execution

#### **Pipelining**

There are many ways of implementing the execution of an instruction. In general, the execution of an instruction can be split into the following phases:

- Instruction fetch: The instruction is fetched from the instruction memory system into a special register.

- Instruction decode: During instruction decode the instruction is interpreted and

passed to an execution unit. This phase can be split into three subparts: decode

(instruction word interpretation), issue (passing the instruction and its operands

to a function unit or to an instruction queue), and dispatch (passing the data for

the actual execution). This terminology is not yet uniform; [HP96] states that

issue and dispatch are sometimes used conversely.

- Execution: The actual calculation or data transfer is performed.

- Writeback: The result of the instruction is written into the register file.

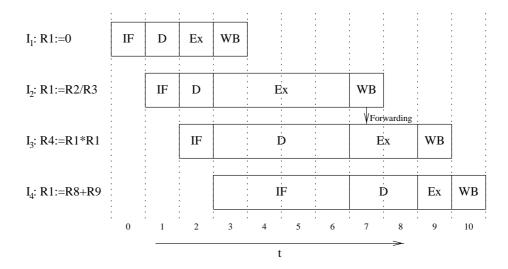

Pipelined CPUs overlap the processing of different phases of different instructions. The first approach is to process the single phases of the instructions strictly in program order. Figure 2.1 illustrates this. Pipelining implies in-order execution, i.e., the execution of the subsequent instructions is also done strictly in program order.

However, in-order execution does not fully utilize all functional parts of a CPU. The rule of in-order execution prohibits that subsequent instructions overtake previous instructions. In figure 2.1, instruction  $I_2$  blocks the execute stage for four cycles, since the division function unit has a long latency. Instruction  $I_3$  has to be stalled upon the begin of its execution, since the execution stage is blocked by  $I_2$  and since it requires the result of  $I_2$  (data dependence).

#### **Out-of-Order Execution**

Data dependencies and different latencies of the function units can cause additional delays which reduce performance. In order to eliminate these delays, the rule of in-order execution of all instruction phases must be dropped. The result is an *out-of-order execution* algorithm. An out-of-order execution algorithm tries to increase performance by distributing the instructions among the available hardware components regardless their original order. There are two main requirements for such an algorithm:

- The algorithm must maintain data consistency.

- The algorithm is supposed to achieve a high utilization of the function units to reduce the delays.

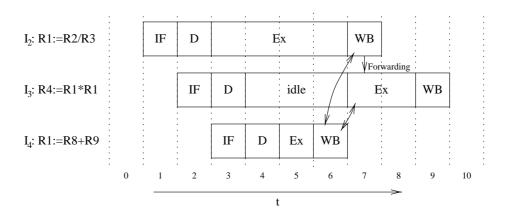

Figure 2.2 depicts the execution of  $I_2$  to  $I_4$  on an out-of-order CPU. Instruction  $I_4$  is now able to enter the execution stage even before  $I_3$  does, since  $I_4$  does not depend on any result of the preceding instructions. It even terminates before  $I_2$ , which causes a write after write (WAW) data hazard in  $R_1$  [HP96].

Furthermore,  $I_3$  tries to read  $R_1$  before  $I_2$  writes it. Thus, there is also a *read after write (RAW) data hazard*. Since  $I_4$  writes  $R_1$  before  $I_3$  reads it, there is also a *write after read (WAR) hazard*.

There are several ways to resolve these hazards. In order to resolve RAW hazards, *result forwarding* is usually used. In the given example, the result of the division is forwarded to instruction  $I_3$ . The scheduling algorithm is supposed to stall the execution of an instruction until all operands are available.

One way to resolve WAW and WAR hazards is to skip the writeback of a result into a register if a subsequent instruction, which writes into the same register, already terminated. In the given example, the writeback of the result of instruction  $I_2$  would have to be skipped. The result is forwarded to instruction  $I_3$  instead. This is implemented by the Tomasulo scheduling algorithm in its original form.

Another way is to delay the result writeback until all previous instructions wrote their result into the register file, i.e., the writeback is performed in-order. This is implemented by the Tomasulo scheduling algorithm with reorder buffer used in this thesis.

### 2.2.2 Basics of the Tomasulo Scheduling Algorithm

The Tomasulo scheduling algorithm has several essential features:

- The Tomasulo scheduling algorithm has a distributed data structure, and requires only few global data.

- The algorithm allows data forwarding wherever possible.

Figure 2.1: Pipelining example

Figure 2.2: Out-of-order execution example. Instructions  $I_2$  and  $I_4$  cause a WAW hazard, instructions  $I_2$  and  $I_3$  cause a RAW hazard, and instructions  $I_3$  and  $I_4$  cause a WAR hazard.

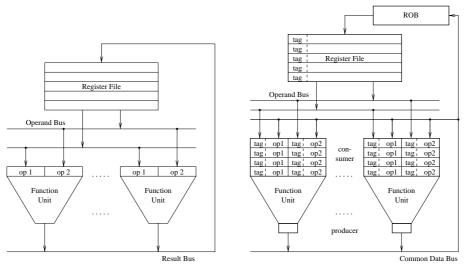

Basic structure of an in-order design

After adding Tomasulo scheduling

Figure 2.3: The basic data structures and data paths before and after adding Tomasulo scheduling

- The algorithm resolves WAW data hazards by inherent register renaming.

- The algorithm has support for function units with variable latency. This includes function units with variable latencies depending on the actual input data values.

Please note that the original Tomasulo algorithm uses out-of-order termination and thus does not support precise interrupts. In order to support precise interrupts, a *re-order buffer* (ROB) [SP88] is added to the machine described in this thesis. The re-order buffer implements in-order termination. This results in small modifications of the original scheduling algorithm. Thus, the following sections describe a modified scheduling algorithm presented in [Ger98] rather than the original Tomasulo scheduling algorithm. The complete protocol is presented in section 2.4, and its hardware implementation is presented in chapter 3.

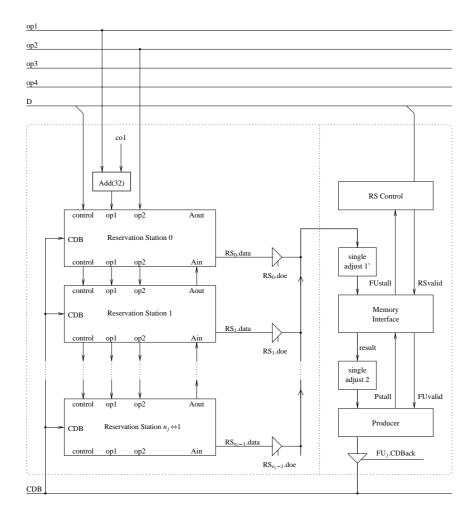

### 2.2.3 Key Data Structures and Transfer Paths

Figure 2.3 gives an overview of the basic data paths of an in-order design and of the same design after adding Tomasulo scheduling with reorder buffer. The Tomasulo scheduling algorithm requires the following data structures and transfer paths:

Each register (named  $\mathbf{R}_i$ .data) is extended by a tag and a valid flag. This extension is called producer table. These additional data fields have the following purposes:

• **R**<sub>i</sub>.valid: The valid flag of a register is set iff the corresponding data item contains the valid value of the register.

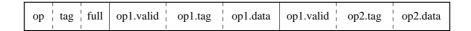

Figure 2.4: Reservation station data items

• **R**<sub>i</sub>.tag: If the valid flag is not set, the tag data item of a register contains a tag for the instruction which produces the desired value.

Each function unit is extended by an instruction buffer to store instructions and operands until all operands and the function unit itself are available. These buffer entries are called **reservation stations**.

The reservation stations provide the operands for the function units. They are basically a queue for the issued instructions. Each reservation station  $RS_i$  holds exactly one instruction and its operands and has the following components (figure 2.4):

- The **RS**<sub>i</sub>.**full** data item is set iff the entry is in use.

- The **RS**<sub>i</sub>.op data item contains additional operation flags. This is, e.g., for an integer ALU, the concrete operation like addition, subtraction, shifting, etc.

- The **RS**<sub>*i*</sub>.tag data item contains the ROB tag of the instruction in the reservation station. This item is an addition to the original Tomasulo algorithm.

- The **RS**<sub>i</sub>.**op**<sub>1</sub> and **RS**<sub>i</sub>.**op**<sub>2</sub> items hold the source operands of the instruction. They are a copy of the appropriate register file and producer table entries and have the same semantics.

The instructions are written into an appropriate reservation station during instruction issue. As soon as all operands of a given instruction in the queue (i.e., in a reservation station) are available, the instruction is ready to be dispatched into the actual function unit.

The result bus of the in-order design is replaced by the *common data bus* (CDB). During instruction dispatch, the instruction is passed to the function unit. On leaving the function unit, the CDB is requested for writing the result on the CDB. Functional units writing on the CDB are called *producers*. Units reading the CDB are called *consumers*. The reservation stations are the usual consumers. They watch the CDB for the operands they are missing (*bus snooping*). However, before a producer can write on the CDB, it has to request the CDB, since multiple producers might try to write on the CDB in the same cycle. These requests are handled by the CDB control, which acknowledges at most one request in the next cycle. <sup>1</sup>

<sup>&</sup>lt;sup>1</sup>In the original Tomasulo design, even two cycles of lead time are required.

| Name  | Width | Purpose                                                       |

|-------|-------|---------------------------------------------------------------|

| valid | 1     | valid = $1 \Leftrightarrow$ data field contains a valid value |

| data  | 64    | result data                                                   |

| dest  | 4     | address of the destination register                           |

Table 2.1: Main components of a reorder buffer entry

## 2.3 The Reorder Buffer

In order to realize precise interrupts, the design in this thesis contains a **reorder buffer** (ROB). Precise interrupts are essential for today's microprocessors. An interrupt between instruction  $I_{i-1}$  and  $I_i$  is precise iff instructions  $I_1,...,I_{i-1}$  are completed before starting the ISR and later instructions ( $I_i,...$ ) did not change the state of the machine [SP88, Mül97b].

On completion, the reorder buffer [SP88] gathers the results produced by the function units and sorts them by issue order, i.e., by program order. The results are written afterwards into the register file in issue order. However, before writing the result of instruction  $I_i$ , it is checked whether this instruction causes an interrupt or not. Thus, in case of an interrupt, the register file contains exactly all modifications made by instructions  $I_0$  to  $I_{i-1}$ .

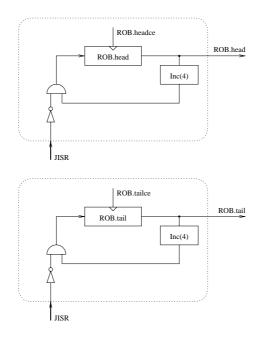

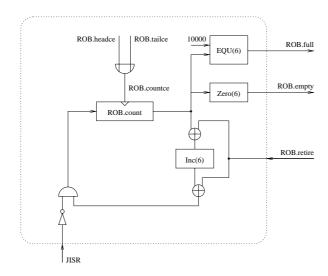

The reorder buffer is realized as circular FIFO queue with a head and a tail pointer. New instructions are put into the ROB entry pointed to by the tail pointer. This ROB address is also used as a tag to the result. This is in contrast to the original Tomasulo design, which uses tags associated with the reservation stations. Table 2.1 lists the main components of a reorder buffer entry. The ROB needs further extensions in order to support interrupts (chapter 3).

When an instruction completes, both the result and the exception flags are written into the reorder buffer entry pointed to by this reorder buffer tag. In each cycle, the entry at the head of the reorder buffer is tested. If it is valid (i.e., the instruction has completed), a check for exceptions is performed and the data is written into the register file. Depending on the type of the interrupt (abort/repeat/continue), the result of  $I_i$  is written into the register file before executing the interrupt service routine.

## 2.4 The Overall Scheduling Protocol

The following section presents the overall scheduling protocol, which is implemented in this thesis [Mül97a, Ger98, Del98]. The execution of an instruction  $I_i$  is split into six phases: fetch, issue, dispatch, execution, completion and writeback.

```

if (\exists free RS for I_i \land \land \land AOB.full)

(1)

RS.op:=I_i;

(2)

RS.full:=1;

RS.tag:=ROB.tail;

\forall operands x of I_i

if (R_{x,A}.valid)

RS.op<sub>x</sub>.valid:=1;

RS.op_x.data := R_{x,A}.data;

initialize

else if (CDB.tag=R_{x,A}.tag)

(5)

reser-

RS.op<sub>x</sub>.data:=CDB.data;

vation

RS.op<sub>x</sub>.valid:=1;

station

else if (ROB[R_{x,A}.tag].valid)

(6)

RS.op_x.data := ROB[R_{xA}.tag].data;

RS.op_x.valid:=1;

else

RS.op_x.tag:=R_{x,A}.tag;

RS.op<sub>x</sub>.valid:=0;

if (I_i has a destination register y.A)

R_{y.A}.tag:=ROB.tail;

ROB[ROB.tail].dest:=y.A;

else

ROB[ROB.tail].dest:=0;

ROB.tail++;

(9)

}

```

Figure 2.5: Issue protocol. The register address of operand x is denoted by x.A.

## 2.4.1 Issue

Let  $I_i$  be the instruction to be issued. For issue, it is essential that an appropriate reservation station and a ROB entry are available ① (figure 2.5). If so, the instruction is issued into this reservation station entry ②. For each operand of the instruction three sources have to be checked ③: The operand might be in the register file ④, on the CDB ⑤, or in the reorder buffer ⑥. If not, it is the destination of a preceding, incomplete instruction ⑦, and instead of the operand, the tag of this instruction is stored in the reservation station.

Simultaneously, the ROB entry is allocated and initialized for the instruction  $\circledast$ . If the instruction has a destination register, the address of this register is stored in the ROB entry and the pointer to the ROB entry is stored as tag in the producer table. After issue, the tail pointer is incremented  $\circledast$ .

Figure 2.6: Dispatch protocol

## 2.4.2 Dispatch

During instruction dispatch (figure 2.6), a valid instruction moves from a reservation station entry into the actual function unit. An instruction is valid iff all its operands are valid ①. Furthermore, the function unit must not be stalled, i.e., it must be ready to accept a new instruction. If more than one instruction for a certain function unit is valid, the scheduler has to choose one for dispatch. The correctness proof in chapter 6 relies on choosing the oldest among the valid instructions. This issue is discussed in chapter 3. If all these conditions hold, the instruction is passed to the function unit ② and the reservation station is freed ③.

In real hardware, RS.opx can also be forwarded via CDB from a producer. In contrast to the forwarding during issue, this forwarding is just an optimization and not necessary for correctness. Thus, this protocol element is omitted here.

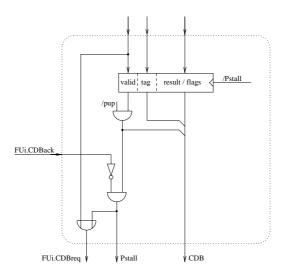

### 2.4.3 Completion

Before completion (figure 2.7), the reservation station requests the CDB. As soon as the reservation station gets an acknowledge ①, the result and the ROB tag are put on the CDB ②. The according reorder buffer entry is filled with the result and the valid bit is set ③.

### 2.4.4 Snooping on the CDB

On completion, the result of an operation is put on the CDB. Instructions in the reservation stations, which depend on this result, read the operand data from the CDB (figure 2.8). The reservation stations identify the results by the ROB tag.

```

if (FU has result \( \) got CDB-acknowledge)

{

CDB.data:=FU.result;

CDB.tag:=FU.tag;

ROB[CDB.tag].valid:=1;

ROB[CDB.tag].data:=CDB.data;

}

```

Figure 2.7: Completion protocol

Figure 2.8: CDB snooping protocol

## 2.4.5 Retirement / Writeback and Interrupts

During retirement (figure 2.9), a result of an instruction in the ROB is written into the register file ③, if no interrupt of type abort or repeat is pending ②.

At the same time, the result flags are checked ④. Almost all result flags are masked with the SR registers prior this check. If an error occurred while processing the instruction, the interrupt service routine is started. Section 3 contains more details of the interrupt mechanism.

## 2.5 Overall Scheduling Example

Figure 2.10 contains an example of Tomasulo scheduling with reorder buffer, considering the following piece of code:

```

I_1: R3 := M[R10]

I_2: R1 := R2 + R3

```

For this example, M[R10] contains the value 11 and R2 contains 9. In cycle t=0, the first instruction is already in the execution phase. It is executed by the memory unit

```

if (ROB is not empty \wedge

(1)

ROB[ROB.head].valid)

if (((ROB[ROB.head].cause \land SR) = 0)

V interrupt is of type continue)

(2)

x := ROB[ROB.head].dest;

R_x.data:=ROB[ROB.head].data;

if (ROB.head=R_x.tag) R_x.valid=1;

}

if ((ROB[ROB.head].cause \land SR) \neq 0)

(4)

Perform Interrupt

else

ROB.head++;

}

```

Figure 2.9: Retirement / writeback protocol

and stored in reorder buffer entry 0. Furthermore, in cycle t=0 the second instruction is fetched.

In cycle t=1, this instruction is decoded and issued into a ALU reservation station. The ALU reservation is assumed to have only one reservation station. The reorder buffer entry 1 is also filled with this instruction.

In cycle t=2, the load instruction is one cycle ahead of completion. Thus, the memory reservation station requests the CDB for the next cycle.

In cycle t=3, this request is acknowledged by the CDB control. The result of the load operation (11) is put on the CDB. This makes the second operand of the ALU reservation station valid. Since both operands are now valid, the instruction is dispatched into the ALU in the same cycle. Furthermore, the ALU requests the CDB for the next cycle. In the same cycle, the result of the load instruction on the CDB is written into the reorder buffer entry 0, which becomes valid.

In cycle t=4, the result of the load instruction is written from the reorder buffer entry 0 into the register file. R3 becomes valid by this. In the same cycle, the CDB control acknowledges the CDB request by the ALU. The result of the addition is put on the CDB and reorder buffer entry 1 becomes valid.

In cycle t=5, this result is finally written into the register file.

|   | ALU reservation station for I <sub>2</sub> |        |      |     |        |      |       | register file |      |       |       |      |     |       |      |       |       |      |

|---|--------------------------------------------|--------|------|-----|--------|------|-------|---------------|------|-------|-------|------|-----|-------|------|-------|-------|------|

| t |                                            | global |      | (   | perand | 1    | op    | erand 2       |      |       | R1    |      |     | R2    |      |       | R3    |      |

|   | op                                         | tag    | full | tag | valid  | data | tag   | valid         | data | tag   | valid | data | tag | valid | data | tag   | valid | data |

| 0 | -                                          | -      | 0    | -   | -      | -    | -     | -             | -    | -     | 1     | 0    | -   | 1     | 9    | ROB-0 | 0     | -    |

| 1 | +                                          | ROB-1  | 1    | -   | 1      | 9    | ROB-0 | 0             | -    | ROB-1 | 0     | -    | -   | 1     | 9    | ROB-0 | 0     | -    |

| 2 | +                                          | ROB-1  | 1    | -   | 1      | 9    | ROB-0 | 0             | -    | ROB-1 | 0     | -    | -   | 1     | 9    | ROB-0 | 0     | -    |

| 3 | +                                          | ROB-1  | 1    | 1   | 1      | 9    | ROB-0 | 1             | 11   | ROB-1 | 0     | -    | -   | 1     | 9    | ROB-0 | 0     | -    |

| 4 | -                                          | -      | 0    | -   | -      | -    | -     | -             | -    | ROB-1 | 0     | -    | -   | 1     | 9    | ROB-0 | 0     | -    |

| 5 | -                                          | -      | 0    | -   | -      | -    | -     | -             | -    | ROB-1 | 0     | -    | -   | 1     | 9    | -     | 1     | 11   |

| 6 | -                                          | -      | 0    | -   | -      | -    | -     | -             | -    | -     | 1     | 20   | -   | 1     | 9    | -     | 1     | 11   |

|   | reorder buffer |          |       |       |     |    |       |       |     |    | common   |     |       |       |      |

|---|----------------|----------|-------|-------|-----|----|-------|-------|-----|----|----------|-----|-------|-------|------|

| t | gloł           | oal      |       | entry | . 0 |    |       | entry | 1   |    | data bus |     |       |       |      |

|   | ROB.head       | ROB.tail | valid | data  | de  | st | valid | data  | de  | st | req      | ack | tag   | valid | data |

| 0 | ROB-0          | ROB-1    | 0     | -     | gpr | R3 | -     | -     | -   | -  | -        | -   | -     | 0     | -    |

| 1 | ROB-0          | ROB-2    | 0     | -     | gpr | R3 | 0     | -     | gpr | R1 | -        | -   | -     | 0     | -    |

| 2 | ROB-0          | ROB-2    | 0     | -     | gpr | R3 | 0     | -     | gpr | R1 | Mem      | -   | -     | 0     | -    |

| 3 | ROB-0          | ROB-2    | 0     | -     | gpr | R3 | 0     | -     | gpr | R1 | ALU      | Mem | ROB-0 | 1     | 11   |

| 4 | ROB-0          | ROB-2    | 1     | 11    | gpr | R3 | 0     | -     | gpr | R1 | -        | ALU | ROB-1 | 1     | 20   |

| 5 | ROB-1          | ROB-2    | -     | -     | -   | -  | 1     | 20    | gpr | R1 | -        | -   | -     | 0     | -    |

| 6 | ROB-2          | ROB-2    | -     | -     | -   | -  | -     | -     | -   | -  | -        | -   | -     | 0     | -    |

Figure 2.10: Scheduling example

## **Chapter 3**

## **Tomasulo Hardware**

## 3.1 Overview

## 3.1.1 Gates, Circuits, Cost and Delay

The hardware model used in this thesis is presented in [MP95]. The following sections just give a really short overview.

For calculation of cost and delay the methods and formulae presented in [MP95] will be used. In particular, the overall calculation is also done by transforming all the complex formulae into a C-program, which is discussed in chapter 5. Thus, cost and delay formulae are omitted in the following chapters.

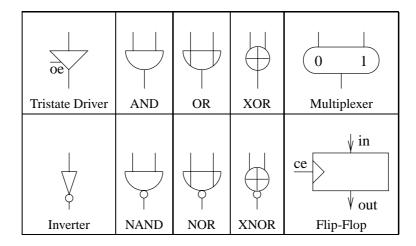

Figure 3.1 lists the symbols of the basic gates used in the designs. In addition, the following basic circuits are used: n-bit adder / incrementer, n-bit multiplexer, tristate driver, n-bit register, n-bit decoder / encoder, n-bit zero tester, the generic parallel prefix circuit, RAM, shifter, and ALU. A detailed description and the cost and delay formulae can be found in [MP95].

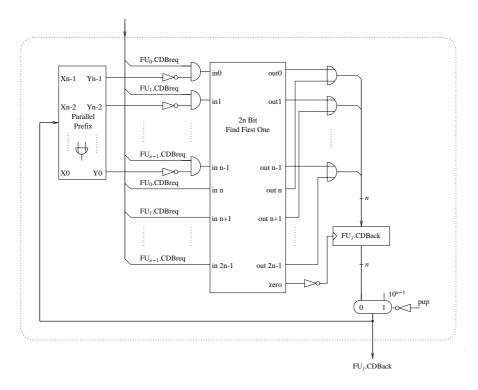

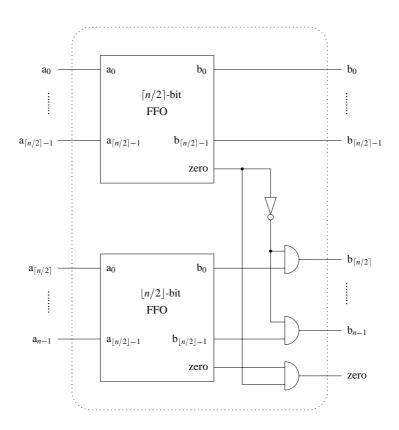

Furthermore, the hardwired control described in this chapter requires two additional basic circuits: the n-bit find first one circuit (FFO) and the find last one circuit (FLO). They calculate the following functions:

$$ffo: \quad \{0,1\}^n \to \{0,1\}^{n+1}, \ (a_{n-1},...,a_0) \mapsto (b_{n-1},...,b_0, \text{zero}), \text{ such that}$$

$$b_i = \left\{ \begin{array}{l} 1 : \quad i = \min\{j | a_j = 1 \land j \in \{0,...,n \Leftrightarrow 1\}\} \\ 0 : \quad \text{otherwise} \end{array} \right.$$

$$\text{zero} = \left\{ \begin{array}{l} 1 : \quad a_i = 0 \text{ for all } i \in \{0,...,n \Leftrightarrow 1\} \\ 0 : \quad \text{otherwise} \end{array} \right.$$

Figure 3.1: Symbols of the basic gates

$$flo: \quad \{0,1\}^n \to \{0,1\}^{n+1}, \ (a_{n-1},...,a_0) \mapsto (b_{n-1},...,b_0, \text{zero}), \text{ such that}$$

$$b_i = \left\{ \begin{array}{l} 1 : \quad i = \max\{j | a_j = 1 \land j \in \{0,...,n \Leftrightarrow 1\}\} \\ 0 : \quad \text{otherwise} \end{array} \right.$$

$$\text{zero} = \left\{ \begin{array}{l} 1 : \quad a_i = 0 \text{ for all } i \in \{0,...,n \Leftrightarrow 1\} \\ 0 : \quad \text{otherwise} \end{array} \right.$$

A recursive construction of the circuits and the cost and delay formulae are given in appendix A.1.

## 3.1.2 The Pipeline Stages

In this chapter, the complete hardware of a DLX RISC core with Tomasulo scheduling is presented. Chapter 4 extends the design with an interface to main memory for load/store operations.

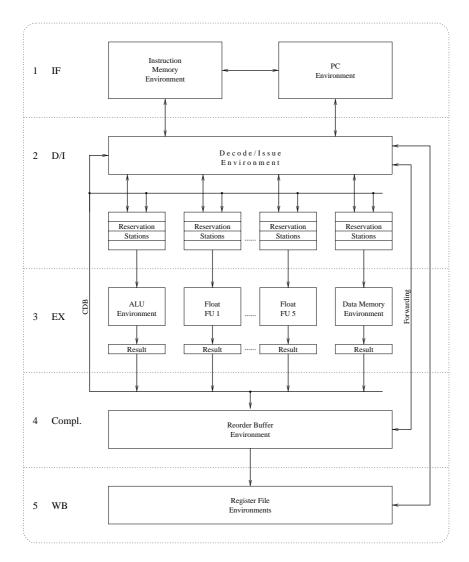

The design is based on the DLX implementations published in [MP95, MP98, Lei98]. It basically consists of a five stage pipeline. The first stage (IF) performs the instruction fetch. In the second stage (D/I), the fetched instruction word is decoded and passed into an appropriate reservation station. The third stage (EX) contains the actual function units, which execute the instruction. Fast function units (i.e., one cycle latency) combine execution and dispatch in one cycle. For slow function units, the execute phase might take several cycles. In the fourth stage (completion), the result of the instruction is stored in the reorder buffer. The fifth stage (WB) performs the writeback of the result into the register file.

3.1. OVERVIEW 17

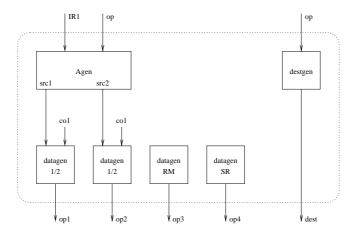

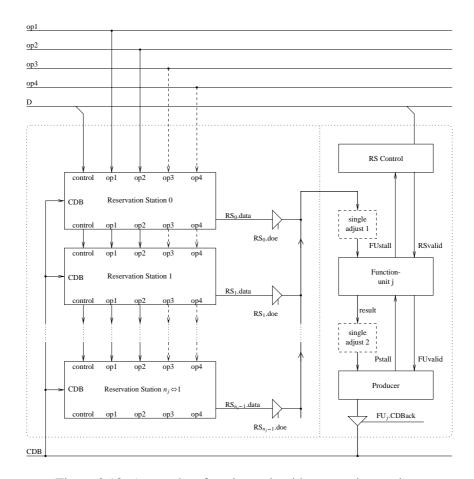

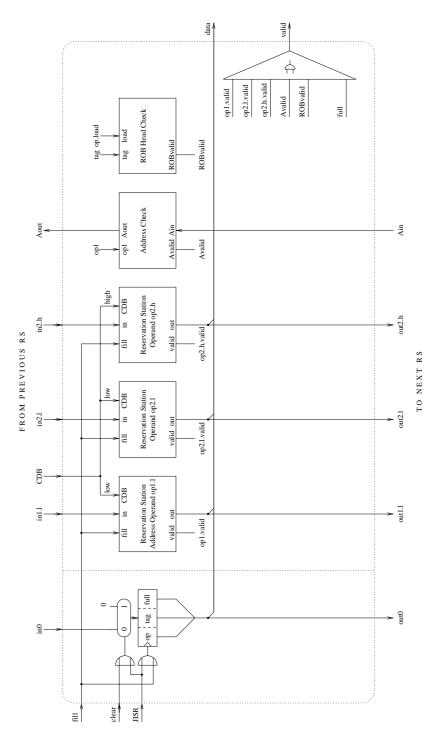

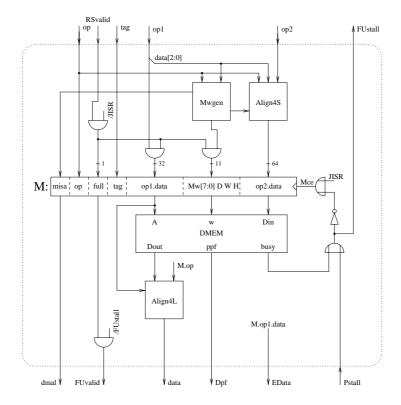

Figure 3.2: Overview of the data paths

## 3.1.3 Environments

The CPU consists of environments. Figure 3.2 gives an overview of the data paths and the interconnection of their environments.

- The **PC environment** contains the PCs of stage 0 and 1 and performs PC calculations.

- The **instruction memory environment** performs the actual instruction fetch and is the interface to the instruction memory or cache.

- The **IR environment** contains the instruction register of the decode/issue stage (IR1).

- The decode/issue environment decodes the fetched instructions and distributes

the instructions among the function units. It also contains the main control automaton.

- Each function unit, including the data memory environment, has its own set of **reservation stations** assigned to it. Each set has an independent control circuit. The reservation station environments belong to the decode/issue stage.

- The **function unit environments** contain the function units, e.g., the ALU, the floating point units, and the data memory interface.

- The **CDB control environment** allocates the CDB to the reservation stations.

- The **reorder buffer environment** contains the reorder buffer and its control circuit. It also contains large parts of the interrupt handling circuitry and belongs to the completion stage.

- The **register file environment** holds the register files and belongs to the write-back stage.

A detailed description of the individual environments follows.

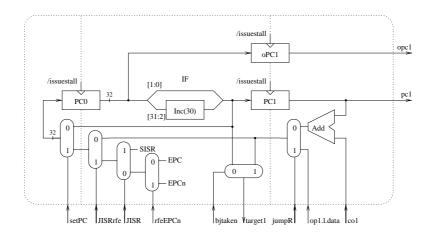

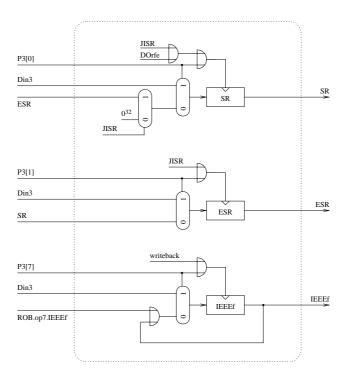

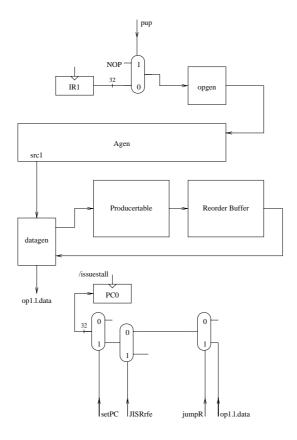

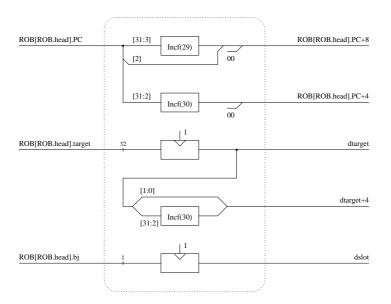

## 3.2 The PC Environment

The PC environment (figure 3.3) contains the program counter PC. It is almost identical with the PC environment found in [Lei98]. The PC register of stage 0 PC0 is used for the instruction fetch (section 3.3). After the instruction fetch, the value of this register is saved in oPC1. Furthermore, the PC environment calculates the new value of the PC register. This is done in dependence of several control signals, which are generated by the main control (section 3.5):

Usually, the new value of the PC0 register is the old value incremented by four. In case of a branch, rfe, jump or an interrupt, the PC register has to be clocked with another value. In these cases, the setPC signal is set. The signal is calculated as follows:

$$setPC = JISRrfe \lor op.branch \lor op.jump \lor op.jumpR$$

The op.branch, op.jump and op.jumpR are active in case of a branch/jump instruction and are calculated by the decode/issue environment. In case of a branch or jump instruction (jumpR=0), co1 (the immediate constant) is the target offset. In case of a jump register instruction (jumpR=1), the signal op1.l.data (low part of the first operand) is the new PC. The operands are provided by the decode/issue environment.

The JISRrfe signal is set iff the cause for the active setPC signal is an interrupt or a rfe instruction. Interrupts are indicated by the JISR signal, which is calculated in the ROB environment. In case of an interrupt, the address of the interrupt service routine (SISR) is clocked into the PC0 register.

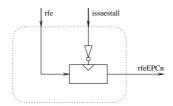

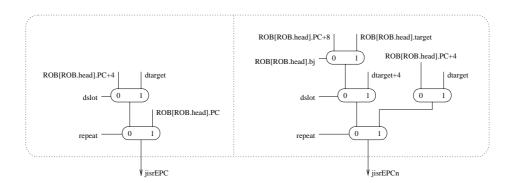

The processing of rfe instructions affects two cycles. In the first cycle after a rfe instruction, the value of the EPC special purpose register is used as address for the instruction fetch. In this cycle, the DOrfe signal is active. This signal is provided by the decode/issue environment. In the second cycle after a rfe instruction, the value of the EPCn register is used. In this cycle, the rfeEPCn signal is active. The signal is the DOrfe signal, which is delayed by one cycle with a register (figure 3.4). Thus, the JISRrfe signal is calculated as follows:

$$JISRrfe = JISR \lor DOrfe \lor rfeEPCn$$

During an issue stall (issuestall=1), all clock enable signals are disabled in order to prevent modifications of the PC registers.

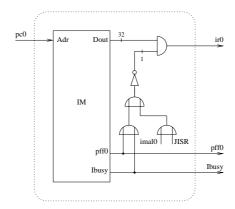

## 3.3 Instruction Memory Environment

The instruction memory environment (figure 3.5) performs the actual instruction fetch and is the interface to the instruction memory or first level instruction cache. The instruction memory environment fetches the instruction word pointed to by the signal pc0, which is provided by the PC environment. This instruction word is returned as signal ir0. Ibusy and pff0 are signals generated by the instruction memory. Ibusy is active iff the instruction memory is temporary unable to return the requested value, e.g., because of a cache miss. The pff0 signal is used to implement virtual memory and indicates a page fault. The instruction memory system only supports word aligned memory accesses. In case of a misaligned access, the imal0 signal is active. It is calculated as follows:

$$imal0 = pc0[0] \lor pc0[1]$$

In case of an interrupt (JISR=1), in case of a misaligned instruction word, or if the instruction memory system is unable to return the requested instruction word, zero is returned instead. This is the opcode for a left shift of register  $R_0$  over 0 bits, thus, it is a NOP instruction.

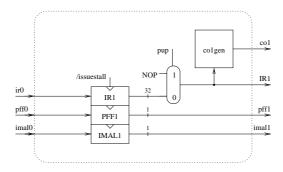

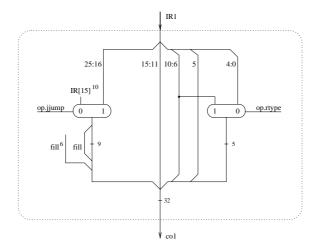

## 3.4 Instruction Register Environment

The instruction register (IR) environment (figure 3.6) contains the instruction register IR1, the page fault register PFF1, and the instruction misaligned register IMAL1 of the decode/issue stage. The instruction register holds the instruction word fetched by the PC environment.

Figure 3.3: PC environment

Figure 3.4: rfeEPCn register

Figure 3.5: Instruction memory environment

21

Figure 3.6: Instruction register environment

Figure 3.7: Immediate constant generation colgen

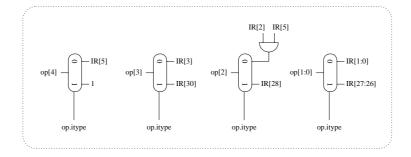

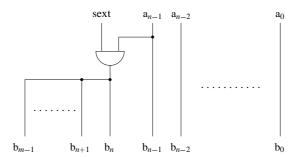

For some instructions, the instruction word provides an immediate constant. The instruction register environment contains the co1gen circuit (figure 3.7), which extracts the immediate constant from the instruction in IR1 and performs a sign extension to 32 bits (signal co1). It is literally taken from [MP95]. The op.jjump and op.rtype signals are generated by the decode/issue environment and are used to determine the width of the constant and the position in the instruction word.

## 3.5 Decode/Issue Environment

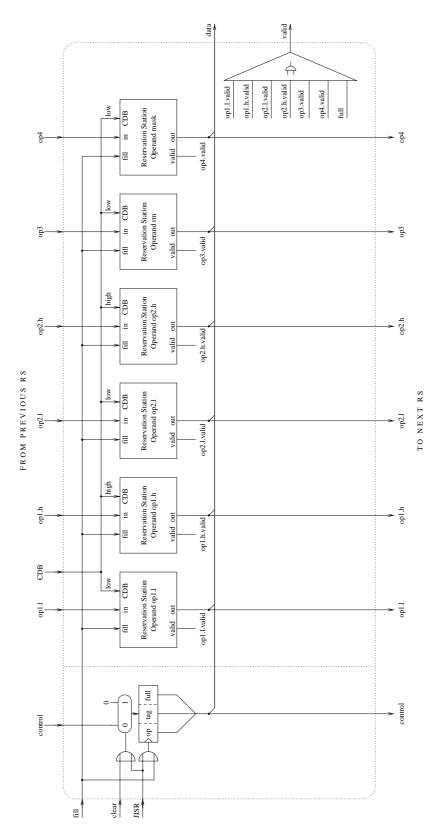

The decode/issue environment serves two purposes: It decodes the instruction word in IR1 and it distributes the instructions and their operands among the reservation stations. A DLX floating point instruction can have up to four source operands (two registers, IEEEf and the interrupt mask), therefore, four operand busses (op1 to op4) originate in the decode/issue environment.

### 3.5.1 Decoding the Instruction Word

The decoding of the instruction word is done by the opgen (operation generation) circuit. The circuit opgen generates several control signals from the instruction word found in IR1 with a control automaton. This environment is almost literally taken from [Lei98]. A figure is omitted therefore.

The automaton has two parts, ID1 and ID2. The first part, ID1, has an automaton state assigned to each instruction. Table 3.1 contains the states and the monomials which are used to compute the new state. The state is never stored in any register, it is just used to compute the active control signals. Table 3.1 also lists the control signals which are active in a given state.

The itype, rtype, and jtype control signals correspond to instruction word formats of the same denominator (appendix C), iuFOP indicates an unimplemented floating point instruction, ill indicates an illegal instruction word. The signals fp and db specify whether floating point (fp=1) or double precision (db=1) values are involved. The signals with names beginning with "FU." indicate the function unit which is required to process the instruction. All other signals specify the action to be performed by this function unit.

Depending on its state, ID1 generates further control signals, which are used to select the correct source and destination operands (table 3.2). For example, op1.RS1 indicates that the register addressed by RS1 is expected on operand bus one. RS1, FS1, RS2, FS2, RD, FD and SA correspond to bit fields in the instruction word, which contain the desired register address (appendix C). R31, FCC, RM and MASK are constant register addresses (table 3.15 contains the coding of the special purpose register addresses). The op2.imm signal is active iff the immediate constant in the instruction word is operand two.

The second part of the automaton, ID2, is only used by branches. In case of a conditional branch, it computes the bjtaken signal, which is active iff the branch is to be taken. If the instruction is not a branch, the signal is undefined. The ID2 automaton requires two input signals: AEQZ and FCCEQZ. AEQZ is active iff the source operand of a conditional branch is zero. FCCEQZ is active iff the FCC bit is zero. Both FCC and the beqz/bnez operand are on the low part of operand bus op1 (table 3.2). Thus, op1.l.data is tested:

AEQZ = zero(op1.l.data[31:0])

$FCCEQZ = \overline{op1.l.data[0]}$

### 3.5.2 Function Unit Availability Test

As mentioned above, the control automaton ID1 determines which function unit is required to process the instruction in IR1. Table 3.3 lists all function units with their

|     | Target                    | Active control                    | Mo         | onomials | S       |

|-----|---------------------------|-----------------------------------|------------|----------|---------|

|     | state                     | signals                           | IR[31:26]  | IR[6]    | IR[5:0] |

|     | ALU                       | rtype, FU.alu                     | 000000     | *        | 0001**  |

|     |                           |                                   | 000000     | *        | 10****  |

|     | Shifti                    | rtype, FU.alu                     | 000000     | *        | 0000**  |

|     | ALUi                      | itype, FU.alu                     | 0*1***     | *        | *****   |

|     | Load                      | itype, load, FU.mem               | 100***     | *        | *****   |

|     | Load.s                    | itype, load, fp, FU.mem           | 110001     | *        | *****   |

|     | Load.d                    | itype, load, fp, db, FU.mem       | 110101     | *        | *****   |

|     | Store                     | itype, store, FU.mem              | 101***     | *        | *****   |

|     | Store.s                   | itype, store, fp, FU.mem          | 111001     | *        | *****   |

|     | Store.d                   | itype, store, fp, db, FU.mem      | 111101     | *        | *****   |

|     | Faddsub.s                 | rtype, faddsub, fp, FU.fadd       | 010001     | 0        | 00000*  |

|     | Faddsub.d                 | rtype, faddsub, fp, db, FU.fadd   | 010001     | 1        | 00000*  |

|     | Fmul.s                    | rtype, fmul, fp, FU.fmul          | 010001     | 0        | 000010  |

|     | Fmul.d                    | rtype, fmul, fp, db, FU.fmul      | 010001     | 1        | 000010  |

|     | Fdiv.s                    | rtype, fdiv, fp, FU.fdiv          | 010001     | 0        | 000011  |

|     | Fdiv.d                    | rtype, fdiv, fp, db, FU.fdiv      | 010001     | 1        | 000011  |

|     | Fcond.s                   | rtype, fcc, fp, FU.ftest          | 010001     | 0        | 11****  |

| ID1 | Fcond.d                   | rtype, fcc, fp, FU.ftest          | 010001     | 1        | 11****  |

|     | Fabsneg.s                 | rtype, fabsneg, fp, FU.fconv      | 010001     | 0        | 00010*  |

|     | Fabsneg.d                 | rtype, fabsneg, fp, db, FU.fconv  | 010001     | 1        | 00010*  |

|     | Ff2i                      | rtype, ff2i, fp, FU.fconv         | 010001     | *        | 001001  |

|     | Fi2f                      | rtype, fi2f, fp, FU.fconv         | 010001     | *        | 001010  |

|     | FMov.s                    | rtype, fmov, fp, FU.fconv         | 010001     | 0        | 001000  |

|     | FMov.d                    | rtype, fmov, fp, db, FU.fconv     | 010001     | 1        | 001000  |

|     | FConv.s                   | rtype, fconv, fp, FU.fconv        | 010001     | *        | 100*00  |

|     | FConv.d                   | rtype, fconv, fp, db, FU.fconv    | 010001     | *        | 100001  |

|     | Branch                    | itype, bjjr, branch, noFU         | 00010*     | *        | *****   |

|     | FBranch                   | itype, bjjr, branch, fp, noFU     | 00011*     | *        | *****   |

|     | JumpReg                   | itype, bjjr, bjtaken, jumpR, noFU | 010110     | *        | *****   |

|     | Jump&LinkReg              | itype, jalr, bjtaken, jumpR, noFU | 010111     | *        | *****   |

|     | Jump                      | jtype, bjjr, bjtaken, jump, noFU  | 000010     | *        | *****   |

|     | Jump&Link                 | jtype, jalr, bjtaken, jump, noFU  | 000011     | *        | *****   |

|     | Trap                      | jtype, trap, noFU                 | 111110     | *        | 000000  |

|     | RFE                       | jtype, rfe, noFU                  | 111111     | *        | *****   |

|     | Movs2i                    | rtype, movs2i, FU.alu             | 000000     | *        | 010000  |

|     | Movi2s                    | rtype, movi2s, FU.alu             | 000000     | *        | 010001  |

|     | FUnimp                    | iuFOP, noFU                       | 010001     | *        | 00011*  |

|     | _                         |                                   | 010001     | *        | 01****  |

|     | Illegal (z <sub>0</sub> ) | ill, noFU                         |            | -        |         |

|     | Taken                     | bjtaken                           | AEQZ · /IF | R1[26]   |         |

|     |                           |                                   | /AEQZ · IF | R1[26]   |         |

| ID2 |                           |                                   | FCCEQZ ·   | /IR1[26  | ]       |

|     |                           |                                   | /FCCEQZ    | ]        |         |

|     | Untaken                   |                                   | /taken     |          |         |

Table 3.1: States, active control signals and DNFs

| State        | Instructions                       | op1. | op2. | op3. | op4. | dest. |

|--------------|------------------------------------|------|------|------|------|-------|

| ALU          | add, sub, test/set, shift          | RS1  | RS2  | -    | -    | RD    |

| ALUi         | addi, subi, test/set immediate     | RS1  | imm  | -    | -    | RD    |

| Shifti       | shift with shift amount            | RS1  | imm  | -    | -    | RD    |

| Load         | load GPR                           | RS1  | -    | -    | -    | RD    |

| Load.s       | load single precision FPR          | RS1  | -    | -    | -    | FD    |

| Load.d       | load double precision FPR          | RS1  | -    | -    | -    | FD    |

| Store        | store GPR                          | RS1  | RD   | -    | -    | -     |

| Store.s      | store single precision FPR         | RS1  | FD   | -    | -    | -     |

| Store.d      | store double precision FPR         | RS1  | FD   | -    | -    | -     |

| Faddsub.s    | fadd.s, fsub.s                     | FS1  | FS2  | RM   | MASK | FD    |

| Faddsub.d    | fadd.s, fsub.s                     | FS1  | FS2  | RM   | MASK | FD    |

| Fmul.s       | fmul.s                             | FS1  | FS2  | RM   | MASK | FD    |

| Fmul.d       | fmul.d                             | FS1  | FS2  | RM   | MASK | FD    |

| Fdiv.s       | fdiv.s                             | FS1  | FS2  | RM   | MASK | FD    |

| Fdiv.d       | fdiv.d                             | FS1  | FS2  | RM   | MASK | FD    |

| Fcond.s      | fc.cond.s                          | FS1  | FS2  | -    | MASK | FCC   |

| Fcond.d      | fc.cond.d                          | FS1  | FS2  | -    | MASK | FCC   |

| Fabsneg.s    | fabs.s, fneg.s                     | FS1  | -    | -    | -    | FD    |

| Fabsneg.d    | fabs.d, fneg.d                     | FS1  | -    | -    | -    | FD    |

| Ff2i         | mf2i                               | FS1  | -    | -    | -    | RS2   |

| Fi2f         | mi2f                               | RS2  | -    | -    | -    | FS1   |

| FMov.s       | mov.s                              | FS1  | -    | -    | -    | FD    |

| FMov.d       | mov.d                              | FS1  | -    | -    | -    | FD    |

| FConv.s      | cvt.s.d, cvt.s.i, cvt.i.s, cvt.i.d | FS1  | -    | -    | -    | FD    |

| FConv.d      | cvt.d.i, cvt.d.s                   | FS1  | -    | -    | -    | FD    |

| Branch       | beqz, bnez                         | RS1  | -    | -    | -    | -     |

| FBranch      | fbeqz, fbnez                       | FCC  | -    | -    | -    | -     |

| JumpReg      | jr                                 | RS1  | -    | -    | -    | -     |

| Jump&LinkReg | jalr                               | RS1  | -    | -    | -    | R31   |

| Jump         | j                                  | -    | -    | -    | -    | -     |

| Jump&Link    | jal                                | -    | -    | -    | -    | R31   |

| Trap         | trap                               | -    | -    | -    | -    | -     |

| RFE          | rfe                                | -    | -    | -    | -    | -     |

| Movs2i       | movs2i                             | SA   | -    | -    | -    | RD    |

| Movi2s       | movi2s                             | RS1  | -    | -    | -    | SA    |

Table 3.2: Operands and bus use

| FU               | Purpose                                  |

|------------------|------------------------------------------|

| FU[0] = FU.alu   | integer instructions, movi2s, movs2i     |

| FU[1] = FU.mem   | load, store                              |

| FU[2] = FU.fadd  | floating point addition and substraction |

| FU[3] = FU.fmul  | floating point multiplication            |

| FU[4] = FU.fdiv  | floating point division                  |

| FU[5] = FU.fconv | conversion floating point / integer      |

| FU[6] = FU.ftest | floating point condition tests           |

Table 3.3: Coding of the function units

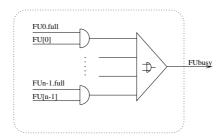

Figure 3.8: Function unit availability test FUtest

purpose and the control signals used to identify them. For each function unit, a single FU[i] is defined in order to simplify notation.

The FUtest circuit of figure 3.8 tests whether this function unit is available. This is done as follows (*n* denotes the number of function units):

$$FUbusy = \bigvee_{i=0}^{n-1} (FU_i.full \land FU[i])$$

The  $FU_i$  full signals are generated by the reservation station controls of the function units.  $FU_i$  full is active iff the reservation stations of the corresponding function unit are not able to accept an instruction.

The signal set  $D.FU_i$  issue specifies the function unit which is actually used for issue. These signals are disabled in case of an issue stall, which is indicated by the issuestall signal.

D.FU<sub>i</sub>.issue = FU[i]

$$\land$$

issuestall  $i \in \{0,...,n \Leftrightarrow 1\}$

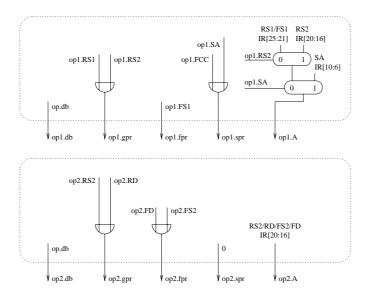

## 3.5.3 Operand Address Generation Agen

The decode/issue environment also provides the operands of the instruction. For the source operands, the values are provided, if available. If they are not available, the

Figure 3.9: Generation of the operands

decode/issue environment provides the appropriate instruction tag to the reservation stations. This is done by the Agen and datagen circuits. For the destination operand, the type and address is determined. This is done by the destgen circuit. Figure 3.9 gives an overview of these circuits.

The operand address generation circuit Agen (figure 3.10) calculates the types and addresses of the source registers. For each operand, the operation generation environment opgen provides signals, which point to bit fields in the instruction word. In turn, these bit fields contain the register addresses of the operands. The type of an operand is represented by five signals:

- The signals opi.fpr, opi.gpr, opi.spr denote the register file which holds the operand, i.e., the floating point, general purpose, and special purpose register file.

- The signal opi.db indicates a double precision floating point register.

- The signal opi.imm is set iff the operand is the immediate constant.

The amount of different operand types is limited for certain operand busses (table 3.2). Operand bus op1 is used for the registers pointed to by RS1 / FS1 (they share the same bit field), RS2 (for mi2f) and SA (for movs2i). Furthermore, it is supposed to provide the value of the FCC special purpose register to process the fbeqz and fbnez instructions. The immediate constant is never on operand bus op1.

The second operand bus op2 has to provide the registers pointed to by RS2 / RD / FS2 / FD (they share the same bit field). Furthermore, it is supposed to provide the immediate constant for ALU operations.

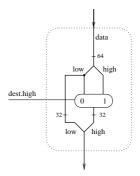

The operand bus op3 is only used for the rounding mode RM, which is required for many floating point instructions. Operand bus op4 is only used for the interrupt

Figure 3.10: Operand address generation Agen

mask, which is also required for floating point instructions. For op3 and op4, no Agen circuit is necessary, since they are always used for the same register.

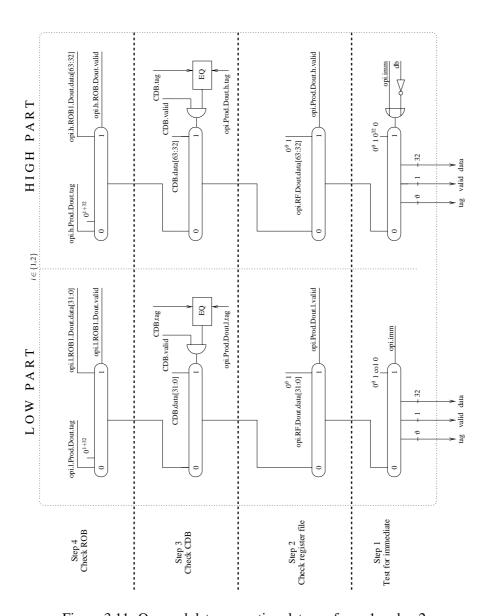

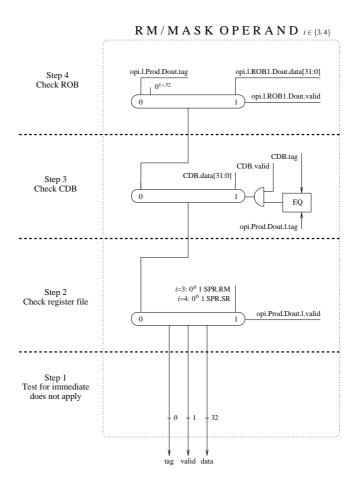

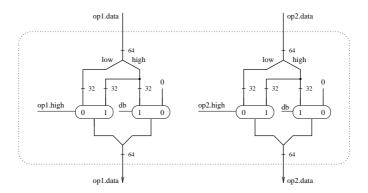

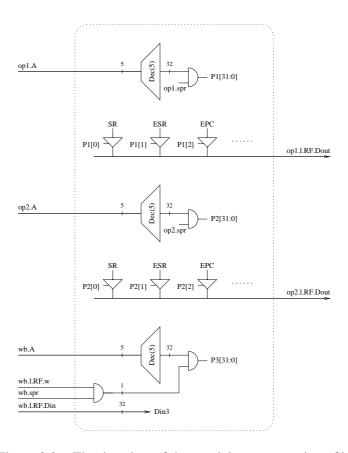

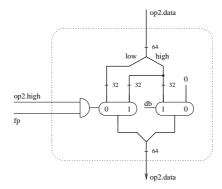

## 3.5.4 Operand Data Generation datagen

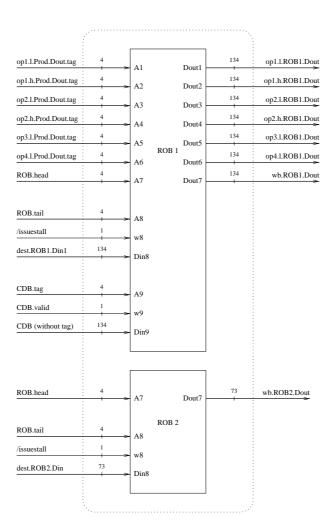

The operand data generation circuits generate the source operands from the addresses and types provided by the Agen circuit. These operands are distributed by four global data paths (table 3.4). The operand busses transport the operands to the reservation stations. Each operand (op1.1, op2.h, op2.1, op2.h, op3.1, op4.1) consists of three components, which are the tag, the valid bit and the operand data (table 3.5),  $\vartheta$  denotes the tag width in bits (section 3.9). Each operand bus has a datagen environment of its own. The environments for op1 and op2 are identical (figure 3.11). The operands three and four do not have a high part and are only used for two fixed special purpose registers. Thus, they have a special datagen environment (figure 3.12) in order to save hardware cost.

The operand data generation environment datagen for op1 and op2 generates one operand according to the signals generated by the operand address generation environment Agen. The low and the high part of the operand are calculated separately, since each part might come from a different source. For each operand and for each part, one of the following cases applies: it is the immediate constant, it is in the register file, it is a result currently on the CDB, it is in the ROB, or it is the result of an instruction which has not yet completed (figure 2.5). Thus, four cascaded multiplexers are used to select the data from the appropriate source.

| Bus | Items | Width                | Purpose                            |

|-----|-------|----------------------|------------------------------------|

| op1 | 1     | $\vartheta + 32 + 1$ | low part of the first operand      |

|     | h     | $\vartheta + 32 + 1$ | high part of the first operand     |

|     | high  | 1                    | lowest bit of the register address |

| op2 | 1     | $\vartheta + 32 + 1$ | low part of the first operand      |

|     | h     | $\vartheta + 32 + 1$ | high part of the first operand     |

|     | high  | 1                    | lowest bit of the register address |

| op3 | 1     | $\vartheta + 32 + 1$ | third operand (always integer)     |

| op4 | 1     | $\vartheta + 32 + 1$ | fourth operand (always integer)    |

Table 3.4: Components of the global data paths

| Item  | Width | Purpose                                                 |

|-------|-------|---------------------------------------------------------|

| tag   | θ     | ROB tag of the instruction producing the operand        |

| valid | 1     | valid = $1 \Leftrightarrow$ operand contains valid data |

| data  | 32    | actual operand data                                     |

Table 3.5: Components of an operand

## **Operand is the Immediate Constant**

The first step is checking whether the operand is the immediate constant (opi.imm=1) or not. If so, the low part of the operand is returned as follows:

$$tag = 0^{\vartheta}$$

$$valid = 1$$

$$data = co1$$

In this case, the operand is valid already during issue. The data value is generated by the colgen circuit (section 3.4). The high part of the operand can never be the immediate constant, thus, it is assumed to be zero in this case to have a defined value on the bus. The high part is also set to zero if the operand is not a double precision floating point value.

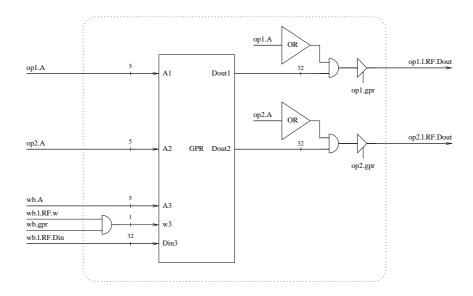

### Operand is in the Register File

If the operand is not the immediate constant, it must be a register. Thus, the second step to get the operand is looking up its valid bit in the producer table. If the valid bit is set, the operand is in the register file. The operand address generation environment provides the necessary address signals opi.A, opi.fpr, opi.gpr, and opi.spr to the register files and to the producer tables, which return the requested values as opi.l/h.RF.Dout (register file) and opi.l/h.Prod.Dout (producer table),  $i \in \{1,...,2\}$ . The registers RM and SR for operand three and four are directly provided by the SPR environment as SPR.RM and SPR.SR.

If the operand part is in the register file (opi.l/h.Prod.Dout.valid=1), the operand bus is set to the following values:

$$\begin{array}{rcl} tag & = & 0^{\vartheta} \\ valid & = & 1 \\ data & = & \left\{ \begin{array}{ll} R[A].data[31:0] & : & low \ part \\ R[A].data[63:32] & : & high \ part \end{array} \right. \end{array}$$

### Operand is on the CDB

If not so (opi.l/h.Prod.Dout.valid=0), the producer table contains the tag of the instruction which produces the desired value. Since this value might be on the CDB in the current cycle, the tag retrieved from the producer table is compared with the tag on the CDB. If both tags are equal and if the valid bit of the CDB is active, the operand is forwarded from the CDB:

$$\begin{array}{rcl} tag & = & 0^{\vartheta} \\ valid & = & 1 \\ data & = & \left\{ \begin{array}{rcl} CDB.data[31:0] & : & low part \\ CDB.data[63:32] & : & high part \end{array} \right. \end{array}$$

### Operand is in the Reorder Buffer

The operand might also be in the reorder buffer. The tag found in the producer table is already the proper index for the ROB to check whether the result is already in the ROB. If so, the valid bit of the ROB entry is set. For this task, ports one to six of the ROB are used. Ports one and two are for op1.1 and op1.h, ports three and four are for op2.1 and op2.h, and ports five and six are for op3 and op4.

```

tag = 0^{\vartheta}

valid = 1

data = \begin{cases} opi.l.ROB1.Dout.data[31:0] : low part \\ opi.h.ROB1.Dout.data[63:32] : high part \end{cases}

```

## Operand is a Result of an Uncompleted Instruction

If none of the cases above applies, the operand must be a result of an uncompleted instruction. The tag of this instruction can be found in the producer table. In this case, the operand is not yet valid and the tag is turned over to the reservation station. The data signal is set to zero in order to have a defined value on the bus.

```

tag = \begin{cases} opi.l.Prod.Dout.tag : low part \\ opi.h.Prod.Dout.tag : high part \end{cases} valid = 0 data = 0^{32}

```

Figure 3.11: Operand data generation datagen for op1 and op2

Figure 3.12: Operand data generation datagen for op3 and op4

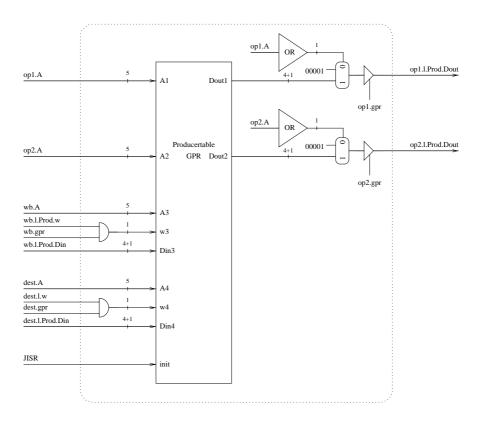

## 3.5.5 Destination Operand Generation destgen

The destination operand generation environment destgen calculates the type and the address of the destination register. This circuit is similar to the address generation environment, which performs the same task for the source operands. The register type of destination is determined according to table 3.2 as:

```

\begin{array}{lll} dest.gpr & = & dest.RD \lor dest.R31 \\ dest.fpr & = & dest.FD \\ dest.spr & = & dest.SA \lor dest.FCC \end{array}

```

The destination is a double precision floating point value if the op.db signal is active or if it is a cvt.s.d or ctv.i.d instruction. These instructions can be distinguished from the other cvt instructions by IR[6] (appendix C).

```

dest.db = op.db \lor (op.fconv \land IR[6])

```

The destination register address is extracted from bit fields of the instruction word (appendix C). The positions of these bit fields depend on the instruction word layout, which is specified by the itype and rtype signals.

```

dest.A = \begin{cases} IR[20:16] & : itype \land (dest.RD \lor dest.FD) \\ IR[15:11] & : rtype \land (dest.RD \lor dest.FD) \\ IR[10:6] & : dest.SA \\ bin(8) (FCC) & : dest.FCC \\ bin(31) (R_{31}) & : dest.R31 \\ 0 & : otherwise \end{cases}

```

### 3.5.6 Stall Generation stallgen

Issue stalls occur if one or more of the following conditions hold:

- 1. For the given instruction, all appropriate reservation stations are busy (FUbusy is active, section 3.5.2).

- 2. The instruction has to be stored in the reorder buffer, but the reorder buffer is full (ROB.full is active, section 3.9).

- 3. If the instruction is a moves2i and the source register is IEEEf, an issue stall is performed until the ROB is empty, to ensure that the register file contains the correct value. This is necessary, since floating point instructions modify the IEEEf special purpose register without any note in the producer table. The signal IEEEfstall is active under this condition:

33

IEEEfstall = op.movs2i

$$\land (IR[10:6] = \underbrace{00111}_{\text{Source}}) \land \overline{\text{ROB.empty}}$$

Alternatively, a check for floating point instructions in the reorder buffer would be sufficient and could increase IPC rates at higher hardware cost.

4. The instruction is a conditional branch or a jump register instruction and the source operand op1 is not yet available. Issuing these instructions would require speculative execution, which is part of a thesis by Mark A. Hillebrand [Hil99]. The signal bstall indicates this stall condition:

bstall=(op.branch

$$\vee$$

op.jumpR)  $\wedge$  op1.l.valid

5. If the instruction is a rfe instruction, an issue stall is required until the ROB is empty. This ensures that the ESR, EPC, and EPCn registers contain the correct values, since they might be modified by an instruction or interrupt prior the rfe instruction. This condition is indicated by the signal rfestall:

rfestall=op.rfe

$$\land \overline{ROB.empty}$$

In the cycle after the stall, DOrfe is activated. This signal causes the actual register transfers, which are done in the PC environment and in the register file environments.

6. The instruction fetch and issue stages have to be stalled if the instruction memory system is busy (IBusy is active) in order to prevent the destruction of the PC registers.

Furthermore, interrupts overrule any issue stall condition. This is done since the instruction, which causes the interrupt, is always ahead of the instruction which causes the issue stall. Thus, the issuestall signal is generated as:

issuestall=(FUbusy  $\vee$  ROB.full  $\vee$  IEEEfstall  $\vee$  bstall  $\vee$  rfestall  $\vee$  IBusy)  $\wedge$   $\overline{\text{JISR}}$

In case of an issue stall, the following actions are performed:

- The instruction fetch is stalled. This is done by disabling the clock enable signals of PC0, PC1, and IR1(section 3.2).

- All D.FU<sub>i</sub>.issue signals are disabled (section 3.5.2) in order to prevent that the instruction is written into a reservation station.

- The instruction is not stored in the reorder buffer (section 3.9).

- The producer table is not modified (section 3.5.5).

Figure 3.13: A complete function unit with reservation stations

# 3.6 The Reservation Station Environments

#### 3.6.1 Overview

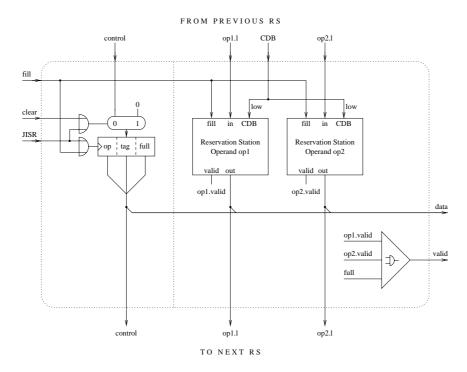

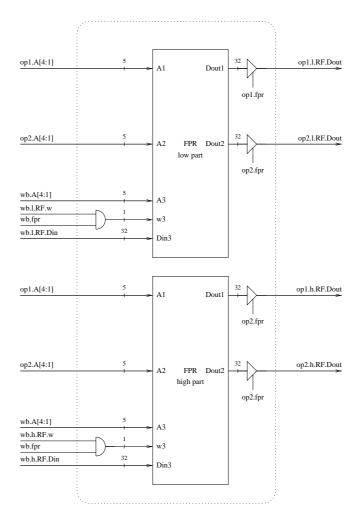

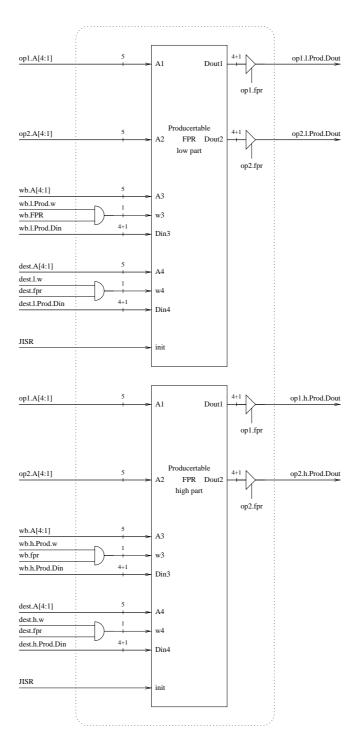

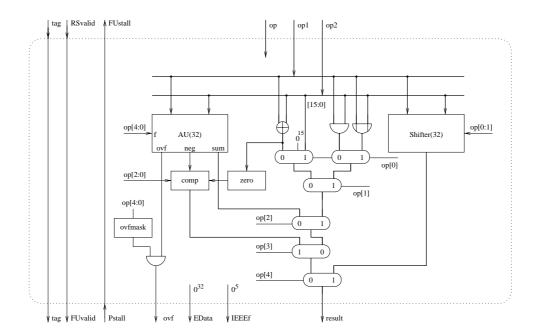

Each function unit has its own set of reservation stations assigned to it. Figure 3.13 gives an overview of a function unit with reservation stations and the producer. The dashed paths and circuits are extensions only needed for floating point function units.

The reservation stations form a queue for instructions and their operands which are provided on the op1 to op4 busses. These busses originate in the decode/issue environment. In each cycle, any desired instruction can move from its reservation station into the function unit. For this purpose, all reservation stations are connected to a bus with tristate drivers. The bus and the reservation stations are controlled by the reservation station control.

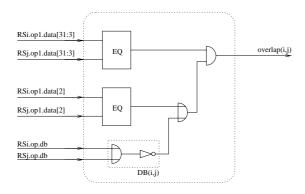

If the function unit is a floating point unit, the data on this bus is adjusted in the single-adjust-one circuit. This circuit makes sure that single precision values are in the lower 32 bits of the bus. After leaving the function unit, the single-adjust-two circuit

makes sure that single precision values are on both lower and higher 32 bits of the bus. After that, the result is propagated on the CDB by the producer circuit.

Integer function units do not need the single adjust circuits. The instruction is passed unmodified to the function unit. After leaving the function unit, the result is passed unmodified to the producer.

# 3.6.2 Operation of the Reservation Stations

As mentioned above, the reservation stations of a function unit j form a queue for the instructions and their operands. Let the queue have  $n_j$  reservation stations. The design in this thesis allows any number of reservation stations. The choice of  $n_j$  only depends on cost effectiveness. Chapter 5 contains a comparison of different assignments.

New instructions are always issued in-order into the first reservation station (reservation station 0). The input values for reservation station 0 are generated by the decode/issue environment.

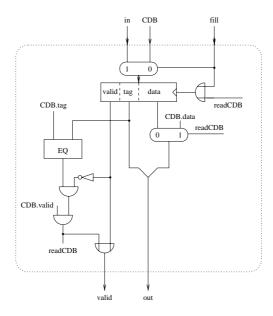

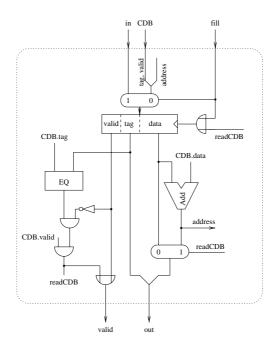

For each operand of an instruction, a valid bit and tag bits are stored in the reservation station. The valid bit is set iff the operand is already in the data item of the reservation station. An instruction in a reservation station is said to be valid if all its operands are available, i.e., valid. If not so, the tag bits hold the tag of the instruction which generates the operand. In this case, the operand circuits snoop on the CDB for the missing operands. The operand circuit compares the tag on the CDB to the tag stored in its register. If both are equal and if the valid bit of the CDB is active, the data item of the CDB is clocked into the data item of the operand.

As soon as one or more instructions in the queue become valid, the oldest among these instructions is dispatched into the function unit and removed from the queue. The reservation station control calculates the necessary output enable signals.

In each cycle, an instruction in reservation station i moves into reservation station i+1, unless reservation station i+1 is full and cannot be freed by moving its content into reservation station i+2 or by dispatching the instruction into the function unit. The reservation station control calculates the necessary clock enable signals.

### **3.6.3** Implementation of the Reservation Stations

Each reservation station can hold the operation code and the operands of one instruction. An implementation of an integer reservation station is given in figure 3.14. The reservation station has a register for the full bit, the tag bits and an operation code op. The full bit indicates that the reservation station is in use. The tag data item is the ROB tag of the instruction in the reservation station. The coding of the op data item depends on the interface to the function unit.

The values in reservation station i are updated if the RS<sub>i</sub>.fill signal is active. The

| ]    | $RS_i.opx$      | $RS_{i-1}.opx$ | new value of        |

|------|-----------------|----------------|---------------------|

| fill | readCDB readCDB |                | $RS_i.opx.data$     |

| 0    | 0               | *              | $RS_i.opx.data$     |

| 0    | 1               | *              | CDB.data            |

| 1    | *               | 0              | $RS_{i-1}.opx.data$ |

| 1    | *               | 1              | CDB.data            |

Table 3.6: Calculation of the new value of a reservation station operand

new values for the reservation station are selected in dependence of the  $RS_i$ .clear signal. If active, the reservation station is filled with an empty entry. If not active, the content of the previous reservation station  $RS_{i-1}$  is copied. The reservation station is also cleared in case of an interrupt, as indicated by the JISR signal. Thus, the content of  $RS_i$  is calculated as follows:

$$RS_i = \begin{cases} \emptyset & : & (RS_i.fill \land RS_i.clear) \lor JISR \\ RS_{i-1} & : & RS_i.fill \land \overline{RS}_i.clear \land \overline{JISR} \\ RS_i & : & \overline{RS}_i.fill \land \overline{JISR} \end{cases}$$

The clear signal only affects the op, tag, and full bits, which are set to zero by a multiplexer. The other registers of the reservation station are not cleared in order to save hardware cost.

Integer function units require two 32 bits wide operands. Each operand has its own box (figure 3.15). Each operand has three components, which are the valid, tag, and data component. The valid bit is set iff the operand is already in the reservation station, i.e., in the data component of the operand register. If not so, the tag bits contains the ROB tag of the instruction which produces the operand. Reservation station operands are updated in two ways: The first way is to copy the content of the same operand in the previous reservation station. This is done iff the fill signal is active. The second way is to copy the content of the corresponding components of the CDB. This is done if the readCDB signal is active, which is calculated as follows:

$$readCDB = (CDB.tag = RS_{i}.opx.tag) \land \overline{RS_{i}.opx.valid} \land CDB.valid$$

If readCDB is active, the reservation station operand provides the new value (i.e., the value on the CDB) as output to the next reservation station and to the function unit. The forwarding of the CDB data is essential for the following reasons: The operand is only one cycle on the CDB. If the data in a reservation station moves into the next reservation station, the operand on the CDB must be written into the next reservation station. Table 3.6 lists how the content of a reservation station operand is calculated.

Furthermore, the valid signal of the reservation station operand becomes active in the same cycle in which readCDB is active. This allows dispatching instructions

Figure 3.14: Reservation station for integer function units

in the same cycle they received their operands via the CDB. This is a performance optimization only and does not affect correctness.

Floating point function units require six operands: two 64 bits wide operands (split into low and high part, respectively) and the rounding mode **rm** and the interrupt mask **mask**. The interrupt mask is needed by the rounder, since the result of an IEEE floating point operation depends on the interrupt mask [Ins85, EP97]. The implementation of the floating point reservation station is identical to the implementation of an integer reservation station except for the additional operands. An implementation of a floating point reservation station is in figure 3.16. The implementation of the operand circuits of a floating point reservation station is identical to the implementation of the operand circuits of an integer reservation station.

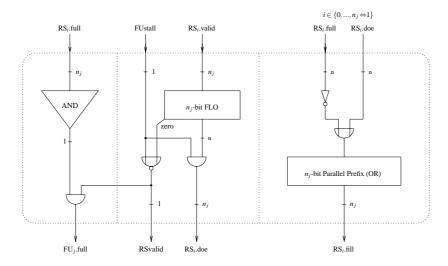

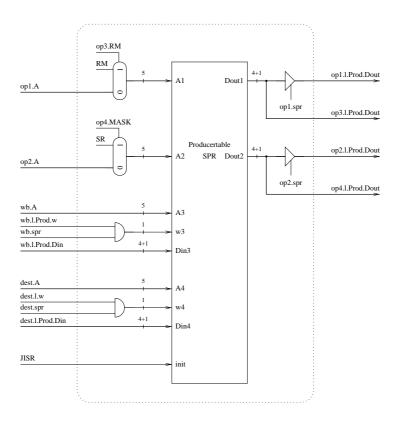

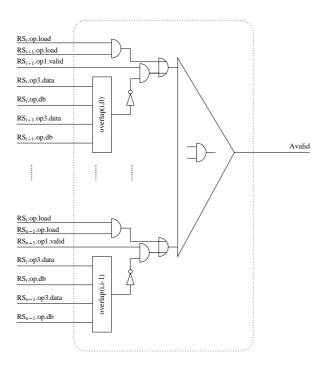

### 3.6.4 Reservation Station Control

#### **Dispatch Control**

The reservation station control (figure 3.17) autonomously governs the dispatch of the valid instructions of the reservation stations into the function unit. Let  $RS_0,...,RS_{n_j-1}$  be the reservation stations of function unit  $FU_j$ .

The  $RS_i$ .doe signal is set iff the instruction in reservation station i is dispatched into the function unit. This transfer is done by a special bus. Each reservation station can

Figure 3.15: Reservation station operand

write on this bus.  $RS_i$ .doe is the output enable signal of the bus driver of reservation station i.

The correctness proof (chapter 6) relies on choosing the oldest among the valid instructions. Since new instructions are always placed in reservation station 0, the oldest valid instruction is obviously in the reservation station with the highest index among the valid reservation stations. Let  $RS_{\alpha}$  be the reservation station which is to become dispatched.

$$\alpha = \max\{i \in \{0, ..., n_i \Leftrightarrow 1\} \mid RS_i.valid=1\}$$

The RS<sub>i</sub>.valid signals are provided by the reservation stations. The max is calculated by a find last one (FLO) circuit (appendix A.1). The circuit returns  $\alpha$  in unary representation. Let  $A_i$  denote this output. The dispatch has to be stalled if the function unit is stalled as indicated by the FUstall signal:

$$RS_i.doe = A_i \wedge \overline{FUstall}$$

At most one of the  $RS_i$  doe signals has to be set in order to prevent bus contention. This is ensured by the find last one circuit.

#### **Flow Control Signals**

The reservation station control generates two flow control signals: The RS valid and  $FU_j$ .full signal.

Figure 3.16: Reservation station for floating point function units

The RSvalid signal is active iff data is dispatched into the function unit. This is true iff there is at least one valid reservation station and the function unit is not stalled. Thus:

RSvalid =

$$\begin{pmatrix} n_j - 1 \\ \bigvee_{i=0} & RS_i.valid \end{pmatrix} \wedge \overline{FUstall}$$

=  $Zero(RS_0.valid,...,RS_{n_i-1}.valid)$  NOR FUstall

The find last one circuit (appendix A.1) has a built-in zero tester, so that the signal can be generated with a single NOR gate.

The  $\mathrm{FU}_j$  full signal is active iff the reservation stations of function unit j are not able to accept an instruction. However, even if all reservation stations of a function unit are full, an instruction can be issued into a reservation station by dispatching one instruction into the function unit if the function unit itself is not stalled.

$$FU_{j}.full = \bigwedge_{i=0}^{n_{j}-1} RS_{i}.full \wedge \overline{RSvalid}$$

In case of an active  $FU_j$ .full signal, the decode/issue environment does not generate a  $FU_j$ .issue signal for the function unit.

#### **Queue Control Signals**

The reservation station control also computes the  $RS_i$ .fill and  $RS_i$ .clear signals. As described above,  $RS_i$ .fill is active iff entry i is to be filled with new values. The  $RS_i$ .clear signal controls whether to clear the reservation station or to copy the data of its predecessor  $RS_{i-1}$ . In case of the first reservation station  $RS_0$ , the data of the predecessor is the instruction provided by the decode/issue environment. The clear signal of a reservation station is only used in the following cases:

- It is used if the entry of the previous reservation station is dispatched and therefore leaves the reservation station queue.

- It is used in case of the first reservation station, if no instruction is issued into the first reservation station.

The calculation of the queue control signals is non-trivial and recursively defined as follows:

$i = n_j \Leftrightarrow 1$ : The last reservation station does not have a successor. It is filled with the data of its predecessor iff its content is dispatched into the function unit  $(RS_{n_j-1}.doe=1)$  or if it is empty  $(RS_{n_j-1}.full=0)$ :

$$RS_{n_j-1}$$

.fill =  $RS_{n_j-1}$ .doe  $\vee \overline{RS_{n_j-1}$ .full

If the content of the predecessor (i.e.,  $RS_{n_j-2}$ ) is dispatched into the function unit, it must not become copied. Thus, the clear signal of the last reservation station is active in this case:

$$RS_{n_i-1}$$

.clear =  $RS_{n_i-2}$ .doe

Table 3.7 contains a list of the possible values.

$i \in \{1,...,n_j \Leftrightarrow 2\}$ : For RS<sub>1</sub> to RS<sub> $n_j$ -2</sub>, the calculation of the RS<sub>i</sub>.fill signal is slightly modified, since these reservation stations have a successor. The signal RS<sub>i</sub>.fill is also active if RS<sub>i+1</sub> takes over the content of RS<sub>i</sub>.

$$RS_i$$

.fill =  $RS_i$ .doe  $\vee \overline{RS_i$ .full  $\vee RS_{i+1}$ .fill

The calculation of the clear signal is identical to the calculation in the previous case.

$$RS_i$$

.clear =  $RS_{i-1}$ .doe

i=0: The first reservation station does not have a predecessor. The input values for the first reservation station are provided by the decode/issue environment. These values are only valid if an instruction is issued into the first reservation station of function unit j. Thus, the reservation station is filled with an empty entry except on issue:

$$RS_0.clear = \overline{D.FU_j.issue}$$

The calculation of the fill signal of reservation station zero is identical to the calculation in the general case.

In order to resolve the recurrency in the formulae of the  $RS_i$ .fill signals, define a set of signals  $F_i(i)$  as:

$$F_i(i) = RS_i.doe \lor \overline{RS_i.full}$$

Now, a closed formula for RS<sub>i</sub>.fill can be specified for  $i \in \{0,...,n_i \Leftrightarrow 1\}$ :

$$RS_{i}.fill = \bigvee_{k=i}^{n_{j}-1} F_{j}(k)$$