# **Automatic Analysis of DMA Races Using Model Checking and k-induction**

Alastair F. Donaldson · Daniel Kroening · Philipp Rümmer

Received: date / Accepted: date

Abstract Modern multicore processors, such as the Cell Broadband Engine, achieve high performance by equipping accelerator cores with small "scratch-pad" memories. The price for increased performance is higher programming complexity – the programmer must manually orchestrate data movement using direct memory access (DMA) operations. Programming using asynchronous DMA operations is error-prone, and DMA races can lead to nondeterministic bugs which are hard to reproduce and fix. We present a method for DMA race analysis in C programs. Our method works by automatically instrumenting a program with assertions modeling the semantics of a memory flow controller. The instrumented program can then be analyzed using state-of-the-art software model checkers. We show that bounded model checking is effective for detecting DMA races in buggy programs. To enable automatic verification of the correctness of instrumented programs, we present a new formulation of k-induction geared towards software, as a proof rule operating on loops. Our techniques are implemented as a tool, SCRATCH, which we apply to a large set of programs supplied with the IBM Cell SDK, in which we discover a previously unknown bug. Our experimental results indicate that our k-induction method performs extremely well on this problem class. To our knowledge, this marks both the first application of k-induction to software verification, and the first example of software model checking in the context of heterogeneous multicore processors.

$\textbf{Keywords} \ \ \text{Model checking} \cdot \textit{k-} \text{induction} \cdot \text{DMA} \cdot \text{multicore programming} \cdot \text{Cell BE}$

This paper is a revised and extended version of [DKR10]. Alastair F. Donaldson is supported by EPSRC grant EP/G051100. Daniel Kroening and Philipp Rümmer are supported by EPSRC grant EP/G026254/1, the EU FP7 STREP MOGENTES, and the EU ARTEMIS CESAR project.

Alastair F. Donaldson

Department of Computer Science, University of Oxford

E-mail: alastair.donaldson@cs.ox.ac.uk

Daniel Kroening

Department of Computer Science, University of Oxford

E-mail: kroening@cs.ox.ac.uk

Philipp Rümmer

Department of Information Technology, Uppsala University

E-mail: philipp.ruemmer@it.uu.se

#### 1 Introduction

Since the late 1950s until early the early 2000s, high-performance computing users (*e.g.* scientists using computers to study complex physical phenomena) have been able to simply wait for consecutive generations of computer hardware to significantly speed up the performance of applications. This was due to the success of *frequency scaling*, facilitated by Moore's law, which states that the number of transistors that can be inexpensively placed on an integrated circuit will double approximately every two years [Moo98].

Although transistor densities continue to double every 18 to 24 months, further increases in processor frequency have been found to lead to prohibitively high levels of power consumption. Instead of increasing the frequency of individual processor cores, manufacturers have opted to deliver performance by using the additional transistors afforded by Moore's law to design processors consisting of *multiple* cores.

In principle, a *homogeneous* multicore processor, consisting of n identical cores which share memory, can offer a factor of n times execution speedup over a single-core processor running at the same clock rate. However, such speedups are rarely achieved for realistic applications, for two main reasons: 1) it may not be possible to partition an application into independent components for parallel execution, and 2) contention for access to shared memory in a data-intensive parallel application may lead to a performance bottleneck. The second problem, known as the *memory wall*, means that even for highly parallel applications, adding further processor cores quickly leads to diminishing returns.

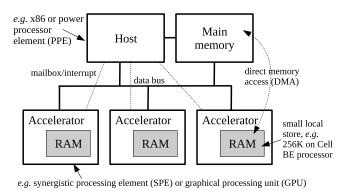

Heterogeneous multicore processors, such as the Cell Broadband Engine (BE) [Hof05, IBM09], circumvent the memory wall problem by equipping cores with small "scratch-pad" memories. These fast, private memories are not coherent with main memory, thus allowing independent calculations to be processed in parallel by separate cores without contention. Movement of data between distinct memory spaces is under software control, and can be coordinated using *direct memory access* (DMA) operations, combined with mailbox/interrupt facilities for inter-core synchronization. A common design for heterogeneous multicore architectures consists of a host core, connected to main memory, together with a number of accelerators each equipped with scratchpad memory. This situation is illustrated in Figure 1.

While the use of scratch-pad memory can boost performance, it places heterogeneous multicore programming at the far end of the concurrent programming spectrum. The programmer can no longer rely on the hardware and operating system to seamlessly transfer data between the levels of the memory hierarchy, and must instead manually orchestrate data movement between memory spaces using *direct memory access* (DMA). Low-level data movement code is error-prone: misuse of DMA operations can lead to *DMA races*, where concurrent DMA operations operate on the same portion of memory, and at least one modifies the memory. If undetected, DMA races can lead to nondeterministic bugs that are difficult to reproduce and fix.

We present a method for DMA race analysis which automatically instruments a C program containing DMA operations with assertions modeling the semantics of a memory flow controller. We consider two different encodings of DMA operations. The first encoding, initially presented in [DKR10], *explicitly* tracks a bounded history of pending DMA operations. DMA races are then detected by comparing each new DMA operation with every pending DMA operation in the history. The second is a novel encoding, sketched in [DHK11], where a single (nondeterministically selected) pending operation is tracked, against which future operations are compared. We call this the *implicit* encoding, because each DMA operation is implicitly compared with every pending DMA operation via a single, arbitrary pending operation. The implicit encoding resembles the concept of *prophecy variables* [AL91] and

permits analysis of programs where an unbounded number of DMA operations may be issued. We show how these encodings can be extended to handle *fence* and *barrier* operations which are supported by architectures such as the Cell BE; the handling of these features is not discussed in [DKR10,DHK11].

The instrumented programs are amenable to automatic verification by state-of-the-art model checkers. A DMA race involves a pair of DMAs either issued by separate threads, or by a single thread. In this paper, we restrict attention to the latter scenario: we focus on analyzing a thread program in isolation, to determine whether the thread can issue simultaneous DMA operations that race with one another. This is an important contribution, since correctly programming a single accelerator thread to issue correct sequences of DMAs is already a significant challenge. Furthermore, this restriction enables scalability: recent dramatic advances in SAT/SMT techniques have led to widespread use of bounded model checking (BMC) [BCC<sup>+</sup>03,CKL04] for finding bugs in sequential software. We show experimentally that applying BMC to instrumented programs yields an effective strategy for detecting DMA races.

As well as detecting DMA races, we are interested in proving their *absence*. However, BMC is only complete if the bound exceeds a completeness threshold [KS03] for the property under consideration, which is often prohibitively large. We overcome this limitation by presenting a novel formulation of *k*-induction [SSS00]. The *k*-induction method has been shown effective for verifying safety properties of hardware designs. In principle, *k*-induction can be applied to software by encoding a program as a monolithic transition function. This approach has not proven successful due to the loss of control-flow structure associated with such a naïve encoding, and because important refinements of *k*-induction (*e.g.* restriction to loop-free paths) are not useful for software where the state-vector is very large.

We present a general proof rule for k-induction that is applicable to imperative programs with loops, and prove correctness of this rule. In contrast to the naïve encoding discussed above, our method preserves the program structure by operating at the loop level. Furthermore, it allows properties to be expressed through assertion statements rather than as explicit invariants. Our experimental results indicate that this method of k-induction performs very well when applied to realistic DMA-based programs, which use double- and triple-buffering schemes for efficient data movement. Such programs involve regularly-structured loops for which k-induction succeeds with a relatively small k.

Experimental evaluation is performed using an implementation of our techniques as a tool, SCRATCH, which checks programs written for the Synergistic Processor Element (SPE) cores of the Cell BE processor. We present an evaluation of SCRATCH using a set of 22 example programs provided with the IBM Cell SDK for Multicore Acceleration [IBM09]. We discover a previously unknown bug in one of these programs, which has been independently confirmed. We compare the explicit and implicit encodings of DMA operations empirically: when proving correctness using k-induction, we find that the implicit encoding is less amenable to k-induction analysis than the explicit encoding; for several examples, the property of DMA race freedom is k-inductive, for a small value of k, only with the explicit encoding. However, in the majority of our experiments, k-induction can successfully prove DMA race freedom with either encoding. In these cases, the implicit encoding leads to significant reductions in verification time, at best providing a 10× speedup for one DMA-intensive benchmark. Our experiments also show the effectiveness of our methods in comparison to predicate abstraction: k-induction allows us to prove programs correct that cannot be verified using current predicate abstraction tools, and bug-finding is orders of magnitude faster. Additionally, SCRATCH is able to find bugs which go undetected by a runtime race-detection tool for the Cell processor.

In summary, our major contributions are:

- an encoding of DMA operations that allows automatic analysis of DMA races in multicore programs with scratch-pad memory. The new encoding presented in this paper builds on an earlier sketch [DKR11], and provides significant speedups over the encoding used in prior work [DKR10].

- a proof rule for k-induction operating on programs with loops, which we show to be effective when applied to a large set of realistic DMA-based programs. On top of the contribution of [DKR10] we present a proof of soundness for our k-induction rule, discuss methods for handling nests of loops, and experimentally compare the relative effectiveness of k-induction for our two encodings of DMA operations.

- SCRATCH, an automatic DMA race analysis tool for the Cell BE processor.

To our knowledge, this line of work marks the first application of k-induction to software verification, and of software model checking to heterogeneous multicore programs.

#### 2 Direct memory access operations

We consider heterogeneous multicore processors consisting of a host core, connected to main memory, and a number of accelerator cores with private scratch-pad memories, as depicted in Figure 1. Each core is equipped with a single scratch-pad memory, to which it has exclusive access. One or more threads can run on each accelerator core, and threads do not migrate between cores during execution. Thus each thread has an associated core. We assume that the accelerator local memories are indexed by disjoint sets of addresses, so that a pointer p refers to a location in the scratch-pad memory of at most one accelerator core. This assumption is for ease of presentation only, and does not hold for some architectures. It would be trivial (but laborious) to adapt our presentation to drop this assumption, identifying a scratch-pad memory location by a pair (c, p), where c specifies a particular accelerator core, and p is an address referring to the scratch-pad memory for c.

A DMA operation  $^{1}$  specifies that a contiguous chunk of memory, of a given size, should be transferred between two memory addresses l and h. The address l refers to accelerator memory (*local store*), and h to main memory (*host memory*). A *tag* (typically an integer value) must also be specified with a DMA; the operation is said to be *identified* by this tag. It is typical for DMA operations to be initiated by the accelerator cores: an accelerator *pulls* data into local store, rather than having the host *push* data. We assume this scenario throughout the paper.

DMA operations are non-blocking – having issued a DMA, an accelerator thread continues executing while the operation is handled by a specialized piece of hardware called a *memory flow controller*. Each accelerator core has its own associated memory flow controller. An accelerator thread can issue a *wait* operation, specifying a tag t. This causes the thread to block until all DMAs being processed by the memory flow controller associated with the thread's core, and identified by t, have completed. A DMA identified by tag t is *pending* until a wait operation with tag t is issued.

The asynchronous nature of DMA operations is essential to achieving high-performance. Several memory movement operations can be executed in parallel, and the latency associated with memory transfers can be hidden by overlapping computation with communication. It is also this asynchronous nature which makes DMA operations hard to program correctly.

<sup>&</sup>lt;sup>1</sup> For brevity, we sometimes write "DMA(s)" rather than "DMA operation(s)".

Although a DMA *may* complete before an explicit wait operation is issued, this cannot be guaranteed. Access (by the host or accelerator) to the region of memory being modified by a pending DMA should be regarded as a bug, as should write access to either region of memory associated with a pending DMA. Failure to issue a wait operation can result in nondeterministic behavior: it may *usually* be the case that the required data has arrived, but occasionally the lack of an explicit wait may result in reading from uninitialized memory, leading to incorrect computation. This nondeterminism means that bugs arising due to misuse of DMA can be extremely difficult to reproduce and fix. This motivates the need for formal analysis techniques to aid programmers in the development of correct DMA-based programs.

# 2.1 DMA primitives and properties of interest

We consider the following basic primitives for DMA operations:

- $\operatorname{put}(l,h,s,t)$ : issues a transfer of s bytes from local store address l to host address h, identified by tag t

- get(l,h,s,t): issues a transfer of s bytes from host address h to local store address l, identified by tag t

- wait(t): blocks until completion of all pending DMA operations identified by tag t

In addition, we consider variants of put and get which allow sequences of DMA operations identified by the same tag to be efficiently synchronized without requiring wait operations:

- putf/getf(l, h, s, t) (put/get with fence): same as put/get, except that the operation will

not commence until all currently pending operations identified by tag t have completed

- putb/getb(l,h,s,t) (put/get with *barrier*): same as put/get, except that the operation, and any future operations identified by tag t, will not commence until all currently pending operations identified by tag t have completed<sup>2</sup>

For each accelerator core, we assume hardware-imposed maximum values M and T for the number of bytes that may be transferred by a single DMA, and the number of distinct tags, respectively. We assume that tags are integers in the range [0, T-1].

We have informally described the notion of memory being corrupted by DMA operations. A special case of memory corruption is where two pending DMAs refer to overlapping regions of memory, and at least one of the DMAs modifies the region of memory. We call this a *DMA race*, and focus our attention on the detection of DMA races for the remainder of the paper. This focus is for ease of presentation only: our techniques can be readily adapted to detect races where the buffer referred to by a pending DMA is accessed by non-DMA statements.

In the remainder of the paper, we use the following predicate:

$$disjoint(a_1, s_1, a_2, s_2) \triangleq (a_1 + s_1 \leq a_2) \lor (a_2 + s_2 \leq a_1)$$

specifying that the memory regions  $[a_1, a_1 + s_1)$  and  $[a_2, a_2 + s_2)$  are disjoint.

<sup>&</sup>lt;sup>2</sup> Note that a barrier operation identified by  $tag\ t$  protects prior operations identified by t from itself and future operations that use  $tag\ t$ . However, the barrier does *not* protect *itself* from such future operations.

**Definition 1** Let  $\mathsf{op}_1(l_1,h_1,s_1,t_1)$  and  $\mathsf{op}_2(l_2,h_2,s_2,t_2)$  be a pair of simultaneously pending DMA operations, where  $\mathsf{op}_1,\mathsf{op}_2 \in \{\mathsf{put},\mathsf{get}\}$ . The pair is said to be *race free* if the following holds:

```

((\mathsf{op}_1 = \mathsf{put} \land \mathsf{op}_2 = \mathsf{put}) \lor \mathsf{disjoint}(l_1, s_1, l_2, s_2)) \land ((\mathsf{op}_1 = \mathsf{get} \land \mathsf{op}_2 = \mathsf{get}) \lor \mathsf{disjoint}(h_1, s_1, h_2, s_2)).

```

The first conjunct in Definition 1 asserts that the local store regions referred to by  $op_1$  and  $op_2$  do not overlap, unless both are put operations (which do not modify local store); the second conjunct asserts that the host memory regions do not overlap, unless both  $op_1$  and  $op_2$  are get operations (which do not modify host memory). We say there is a *DMA race* when some pair of pending DMA operations is not race free.

The conditions for race freedom with fence and barrier operations are more complex, and are discussed in detail in §5.4.

## 2.2 DMA operations in the Cell BE processor

The Cell BE processor [Hof05, IBM09] is a heterogeneous multicore architecture consisting of a host Power Processor Element (PPE) core, together with 8 accelerator cores, known as Synergistic Processor Elements (SPEs). The PPE is a regular CPU core connected to a large main memory, whereas the SPE cores are fast vector processors, each equipped with a 256K scratch-pad memory. As discussed in §1, these scratch-pad memories are *not* coherent with main memory, and SPE software must use DMA operations to transfer data between scratch-pad memory and main memory.

Each SPE is equipped with a memory flow controller supporting up to 16 concurrent DMA operations, which may be executed out-of-order. If an SPE attempts to issue a DMA operation when the hardware limit of 16 concurrent operations has been reached, SPE execution stalls until some DMA operation completes.

The maximum amount of data that can be transferred by a single DMA operation is 16K, thus M=16384. The number of distinct tags, T, is 32. This allows a set of tags to be represented using a 32-bit word.

## 2.3 Illustrative example: triple-buffering

Figure 2, adapted from an example provided with the IBM Cell SDK [IBM09], illustrates the use of DMA operations to stream data from host memory to local store to be processed, and to stream results back to host memory. Triple-buffering is used to overlap communication with computation: each iteration of the loop in triple\_buffer puts results computed during the previous iteration to host memory, gets input to be processed next iteration from host memory, and processes data which has arrived in local memory.

If  $num\_chunks$  is greater than three, this example exhibits a local store DMA race, which we can observe by logging the first six DMA operations. To the right of each operation we record its source code location and, if appropriate, its loop iteration. We omit host address parameters as they are not relevant to the data race.

```

get(buffers[0], ..., CHUNK, 0) (1)

get(buffers[1], ..., CHUNK, 1) (2)

wait(0) (3)

(*) put(buffers[0], ..., CHUNK, 0) (4), i=2

get(buffers[2], ..., CHUNK, 2) (5), i=2

wait(1) (6), i=2

put(buffers[1], ..., CHUNK, 2) (4), i=3

(*) get(buffers[0], ..., CHUNK, 0) (5), i=3

```

At this point in execution the operations marked (\*) are both pending, since the only intervening wait operation uses a distinct tag. The operations are not race free according to Definition 1 since they use the same region of local store and one is a get. The race can be avoided by inserting a wait with tag tags[get\_buf] before the get at (5), or replacing the get at (5) with a getf operation.

We discovered this bug using SCRATCH, our automatic DMA analysis tool, described in §7, which can also show that the fix is correct. The bug occurs in an example provided with the IBM Cell SDK, and was, to our knowledge, previously unknown. Our bug report via the Cell BE forum has been confirmed by IBM engineers. In the remainder of the paper, we present the techniques employed by SCRATCH to enable these results.

#### 3 Overview of our method

We present a DMA race analysis technique geared towards verification of a single single accelerator thread, which may be running as part of a concurrent application. Our method can detect races between multiple DMA operations issued by the same accelerator thread, but not races between operations issued by distinct threads. Because an accelerator thread can issue many concurrent DMA operations, writing correct code for a single thread can be challenging, as demonstrated by the triple-buffering example of §2.3. Providing a DMA race analysis technique for sequential software is thus an important contribution. Restricting the analysis to consider a single thread enables a scalable method, avoiding the state-space explosion associated with multiple thread interleavings. Nevertheless, the detection of DMA races between multiple threads remains an important problem; in §9 we discuss plans for future work in this area.

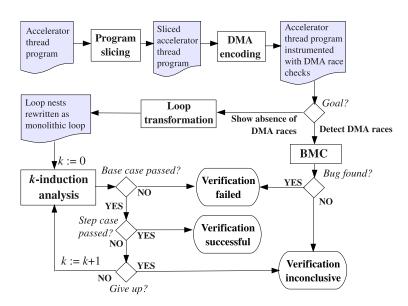

Our method is summarised by the flowchart of Figure 3, and has been implemented, for the Cell BE processor, in the SCRATCH tool (see §7). We now discuss the various components of this flow-chart.

*Program slicing.* Typically, programs for scientific or media-processing computation contain a significant amount of intricate code that is irrelevant to the way in which DMA is used to transfer data between host and accelerator memory. To remove as much of this detail as possible, we first perform program slicing, reducing the program code to the DMA-relevant statements.

Encoding DMA operations. After slicing, the program is instrumented with assertions that check the conditions required for a DMA race to occur. Instrumentation depends on an appropriate encoding of DMA operations; in §5 we present two encoding schemes, which are implemented in SCRATCH. Once instrumentation is complete, the resulting program can be analysed in an attempt to reveal potential DMA races, or prove their absence.

Bounded model checking, for detection of DMA races. If a program is suspected to give rise to a DMA race, then BMC techniques [BCC<sup>+</sup>03] can be applied to search for races up to a

user-specified execution depth. SCRATCH uses CBMC [CKL04], a bounded model checker for C programs, for this purpose. If CBMC finds a violation of an assertion introduced by DMA instrumentation then the corresponding counterexample demonstrates how a DMA race may manifest.

Proving absence of DMA races using k-induction. Alternatively, our method can attempt to prove DMA race-freedom for a program using the k-induction technique, applied at the level of program loops. In  $\S 6$ , we present a proof rule for k-induction which operates on a *single* loop. This rule can be applied to programs containing multiple loops by first rewriting all program loops as a single, monolithic loop, using a standard technique [Har80] which we recap in  $\S 7$ . This is the *loop transformation* stage in the flowchart of Figure 3.

Applying k-induction involves checking a base case and a step case for a given value of k. Our k-induction rule guarantees that these are straight-line programs, whose correctness can be established in a straightforward manner. SCRATCH invokes CBMC for such checks. If the base case fails, this indicates that the program can give rise to a DMA race, and a counterexample is reported. If both the base and step cases pass, soundness of our k-induction rule (proved in  $\S 6$ ) means that the program has been shown to be free of DMA races. Otherwise, in the case where the base case passes but the step case fails, there are two options: the verification attempt can be abandoned, or a larger value of k can be tried.

**Extent of automation.** While SCRATCH attempts to perform automatic analysis of SPE programs for the Cell BE processor, we do not describe the tool as *fully* automatic, for two reasons. First, SPE programs typically make heavy use of single instruction multiple data (SIMD) intrinsic functions that are specific to the Cell architecture. The prototype SCRATCH tool does not support reasoning about this large set of functions, thus program slicing is performed manually in our experiments. However, it can in principle be automated. Second, and more crucially, the success of k-induction in automatically producing a conclusive verification result is largely dependent on the strength of assertions appearing in the program text. As discussed in §6.2, and demonstrated experimentally in §7, our encodings of DMA operations usually lead to assertions that are inductive already for small values of k. However, in some of our experiments, it proved necessary to supply additional strengthening assertions by hand. In related work we have shown that such assertions can often be inferred automatically using abstract interpretation [DHK11].

## 4 Goto programs

We present our results in terms of a simple goto language, which is minimal, but general enough to uniformly translate C programs like the one in Figure 2. The syntax of the goto language is shown in the following grammar, in which  $x \in X$  ranges over integer variables,  $a \in A$  over array variables,  $\phi$  and e over boolean and integer expressions (for which we do not define syntax, assuming the standard operations), and  $l_1, \ldots, l_k \in \mathbb{Z}$  over integers:

$$\begin{array}{lll} \textit{Prog} \; ::= \; 1: \; \textit{Stmt}; \ldots; n: \; \textit{Stmt} & \textit{VarRef} \; ::= \; x \; \big| \; a[e] \\ \textit{Stmt} \; ::= \; \textit{VarRef} \; := * \; \big| \; \text{assume} \; \phi \; \big| \; \text{goto} \; l_1, \ldots, l_k \end{array}$$

A goto program is a list of statements numbered from 1 to n.

The language includes assertions, nondeterministic assignment (VarRef := \*), assumptions (which can constrain variables to specific values), and nondeterministic gotos. Execution of a goto statement, which is given a sequence of integer values as argument (the goto

targets), causes the value of one of these (possibly negative) integers to be added to the instruction pointer. We use x:=e and a[i]:=e as shorthands for assignments to variables and array elements, respectively, which can be expressed in the syntax above via a sequence of nondeterministic assignments and assumptions. For simplicity, we assume variables and array elements range over the mathematical integers,  $\mathbb{Z}$ ; when translating C programs into the goto language the actual range of variables will always be bounded, so SAT-based analysis of goto programs by means of bit-blasting is possible.

The transition system described by a program  $\alpha=1:\alpha_1;\ldots;n:\alpha_n$  is a graph  $(S,E_\alpha)$ , where S is the set of program states and  $E_\alpha$  the transition relation. Program states are given by the set

$$S = \{ (\sigma, pc) \mid \sigma : (X \cup (A \times \mathbb{Z})) \to \mathbb{Z}, \ pc \in \mathbb{Z} \} \cup \{ \xi \}$$

in which  $\sigma$  is a store mapping variables and array locations to integer values, pc is the instruction pointer, and  $\xi$  is a distinguished state that designates erroneous termination of a program.

We write  $t^{\sigma}$  for the value of an expression given the variable assignment  $\sigma$ , denote the set of all storage locations by  $L = X \cup (A \times \mathbb{Z})$ , and define tt, ff to be the truth values of boolean expressions. The set of transitions  $E_{\alpha}$  is as follows:

$$\begin{split} E_{\alpha} &= \{(\sigma, pc) \rightarrow (\sigma', pc+1) \mid \alpha_{pc} = x := *, \ \forall l \in L \setminus \{x\}. \ \sigma(l) = \sigma'(l)\} \\ & \cup \{(\sigma, pc) \rightarrow (\sigma', pc+1) \mid \alpha_{pc} = a[e] := *, \ \forall l \in L \setminus \{(a, e^{\sigma})\}. \ \sigma(l) = \sigma'(l)\} \\ & \cup \{(\sigma, pc) \rightarrow (\sigma, pc+1) \mid \alpha_{pc} = \text{assume } \phi, \ \phi^{\sigma} = tt\} \\ & \cup \{(\sigma, pc) \rightarrow (\sigma, pc+1) \mid \alpha_{pc} = \text{assert } \phi, \ \phi^{\sigma} = tt\} \\ & \cup \{(\sigma, pc) \rightarrow \frac{\iota}{\ell} \mid \alpha_{pc} = \text{assert } \phi, \ \phi^{\sigma} = ff\} \\ & \cup \{(\sigma, pc) \rightarrow (\sigma, pc+l_i) \mid \alpha_{pc} = \text{goto } l_1, \dots, l_k, \ i \in \{1, \dots, k\}\} \end{split}$$

If the context  $\alpha$  is clear, we just write  $s \to s'$  for the membership  $(s \to s') \in E_{\alpha}$ .

Proper termination of  $\alpha$  in a state s is denoted by  $s\downarrow$  and occurs if the instruction pointer of s does not point to a valid statement:  $s\downarrow \equiv s=(\sigma,pc)\land pc\not\in [1,n].$  Note that no transitions exist from states s with  $s\downarrow.$

The set  $traces(\alpha)$  of (finite and infinite) traces of a program  $\alpha$  is defined in terms of its transition system:

$$traces(\alpha) = \left\{ s_1 \, s_2 \, \cdots \, s_k \mid \exists \sigma. \, s_1 = (\sigma, 1), \, s_k \downarrow \text{ or } s_k = \not \downarrow, \\ \forall i \in \{1, \dots, k-1\}. \, s_i \to s_{i+1} \right\}$$

$$\cup \left\{ s_1 \, s_2 \, \cdots \mid \exists \sigma. \, s_1 = (\sigma, 1), \, \forall i \in \mathbb{N}. \, s_i \to s_{i+1} \right\}$$

In particular, no traces exist on which assumptions fail.<sup>3</sup> A program  $\alpha$  is considered *correct* if no trace in  $traces(\alpha)$  terminates erroneously, *i.e.* no trace contains  $\frac{1}{2}$ .

## 5 Encoding DMA operations in goto programs

We now consider the goto language extended with the DMA primitives of §2.1:

$$\begin{split} \mathit{Stmt} \; ::= \; \dots \; \big| \; & \mathsf{get}(e,e,e,e) \; \big| \; \mathsf{put}(e,e,e,e) \; \big| \; & \mathsf{getf}(e,e,e,e) \; \big| \; & \mathsf{putf}(e,e,e,e) \\ & \big| \; & \mathsf{getb}(e,e,e,e) \; \big| \; & \mathsf{putb}(e,e,e,e) \; \big| \; & \mathsf{wait}(e) \end{split}$$

<sup>&</sup>lt;sup>3</sup> In our context, this is preferable to modeling failed assumptions via a distinguished "blocked program" state: it simplifies the notion of sequential composition of programs (*cf.* §6.1).

We present two methods for translating a goto program in this extended language to a standard goto program, replacing DMA operations with suitable instrumentation code such that a potential DMA race results in a failed assertion.

In §5.1 we present an explicit encoding, where DMA races are analyzed by logging a bounded history of previously pending operations. This is the encoding used in [DKR10]. We then present, in §5.2, a new, implicit encoding where a single pending DMA operation is selected nondeterministically for tracking. This allows analysis of programs which may issue an unbounded number of DMA operations.

We choose the names *explicit* and *implicit* for our encodings because the first encoding detects a DMA race by comparing a newly issued DMA explicitly with every pending DMA, while the second encoding performs this comparison implicitly, by comparing the newly issued DMA with a single, arbitrary pending DMA.

In §7 we show experimentally that the implicit encoding can provide significant improvements in verification time over the explicit encoding. We illustrate the difference between these approaches using examples in §5.3.

In both cases, we do not initially present details of the way fence and barrier operations are encoded. In §5.4 we show how this is achieved for the implicit encoding (a similar approach can be applied to the explicit encoding).

#### 5.1 An explicit encoding

Our goal is to ensure that, during program execution, a thread does not issue a DMA that races with another DMA issued previously by the thread. Suppose, for a given program, we have an upper bound D on the number of DMAs that may be concurrently pending. In this case, we can check the conditions for a DMA race by explicitly logging the set of DMAs that are concurrently pending during program execution. This requires recording a history of at most size D. When a new DMA is issued, we first assert that the operation does not race with any existing DMA. We then assert that the size of the set of concurrently pending DMAs is smaller than D. Finally, we add the new DMA to the log. A wait operation of the form wait(t), where t is a tag, is encoded by removing from the log any DMA identified by tag t.

The log of DMA operations is encoded as a series of *tracker arrays*, as follows, with  $0 \le i \le D$ :

- valid: valid[j] = 1 if values at position j in the other arrays are being used to track a DMA, otherwise valid[j] = 0 and values at position j in the other arrays are meaningless

- $is\_get$ :  $is\_get[j] = 1$  if the j-th tracked DMA is a get, otherwise  $is\_get[j] = 0$

- local, host, size, tag: element j records the local store address, host address, size and tag of the j-th tracked DMA, respectively

Figure 4 shows how a program with basic DMA primitives can be translated into a standard goto program, where get, put and wait operations are replaced with assertions and assignments over the tracker arrays. The translation makes use of the disjoint predicate, defined in §2.1. We use  $\forall_{0 \leq j < D}$  Stmt to indicate that Stmt should be duplicated D times with increasing values for j. Note that, because D is fixed at translation time, this leads to D consecutive statements, rather than the generation of a loop. Since the rules of Figure 4 replace single statements with multiple statements, it is necessary to perform a re-numbering of program statements and goto targets after translation; we omit details of this re-numbering.

The encoding of DMAs is based on Definition 1, and is designed to prohibit the issue of DMAs that are simultaneously pending but not race free. Note that in our simple goto language we do not model actual movement of data via DMA. In practice, to achieve soundness, we must set the memory locations written to by a DMA operation to nondeterministic values.

This explicit encoding is natural as it mirrors the idea of runtime logging of DMA operations, which is performed for example by the IBM Race Check library [IBM08]. The disadvantage of the encoding is that it depends on the existence of a limit, D, for the number of DMAs that may be concurrently pending in a given program. The cost of the encoding increases proportionally with D. This can lead to scalability issues when analyzing instrumented programs using SAT-based bounded model checking. Furthermore, the encoding does not allow reasoning about programs that may issue an arbitrary number of simultaneous DMAs.

## 5.2 A more efficient, implicit encoding

We now present a more efficient encoding of DMA operations which does not require the upper limit *D*. This encoding allows us to analyze programs which may issue an unbounded number of DMAs.

The key insight which leads to a more efficient encoding is the fact that checking for DMA races only requires pairwise consideration of DMA operations. In translating put and get in Figure 4, we use a universal quantifier to compare the new DMA operation against every previously issued DMA operation that is still live. Observe that it suffices to nondeterministically record details of a single, arbitrary DMA operation, and check further operations for races with respect to this operation. A wait operation of the form wait(t) can be encoded by an assumption that the currently tracked DMA (if any) does not have associated tag t. In other words, the encoding ensures that we discard execution traces along which it was chosen to track, and subsequently wait for completion of, a given DMA operation. This approach resembles the concept of  $prophecy\ variables\ [AL91]$ , since the future program execution determines whether a DMA operation should be tracked or not. As discussed above, we call this encoding implicit because a new DMA is implicitly compared with all pending DMAs by tracking a single, arbitrary pending DMA.

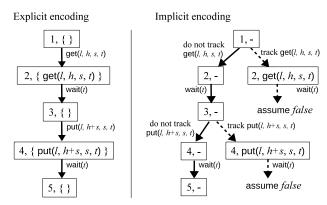

Translation rules for this implicit encoding are presented in Figure 5. Note that valid, local, host, size and tag are no longer arrays: they are now scalar variables that collaboratively track a single DMA operation when valid = 1. For clarity in the translation rules, we use labels track and after to denote the targets of a nondeterministic goto statement, rather than explicit integer offsets to the instruction pointer as the goto program syntax of  $\S 4$  strictly requires.

The encoding of Figure 5 is more compact than the explicit encoding of Figure 4, since it involves tracking just one DMA operation, rather than an array of D operations. In  $\S 7$  we demonstrate experimentally that the implicit encoding results in faster verification compared with the explicit encoding.

## 5.3 Examples

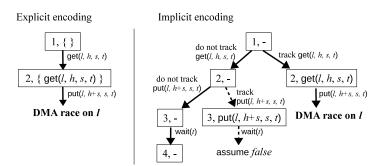

We illustrate the difference between the explicit and implicit encodings using the simple examples of Figure 6.

The program of Figure 6(a) is clearly race-free: the get operation identified by tag t is immediately followed by a wait operation using tag t, ensuring that the get operation completes before the put operation at line 3 commences. The left-hand-side of Figure 7 illustrates the transition system corresponding to this program when DMA operations are translated using the explicit encoding of Figure 4. Each rectangle represents a state, labeled with a program counter location followed by a set of pending DMA operations. The figure illustrates that, as the program is executed, the set of tracked DMAs is modified accordingly. The right-hand-side of Figure 7 illustrates the corresponding transition system when the implicit encoding of Figure 5 is used. Dashed lines are used to illustrate paths through the transition system which end in failed assumptions, thus not forming part of the set of program traces. States are labeled by a program counter location followed by details of a single tracked DMA operation, with '-' used to represent the case where no operation is tracked (i.e. when valid = 0). From the initial state, a nondeterministic choice determines whether operation get(l, h, s, t) is tracked. The right-hand branch represents the case where this operation is tracked. The encoding of the wait(t) operation assumes that no operation with tag t is tracked, invalidating this branch. As a result, the only valid state from which put(l, h + s, s, t) can be executed is the state [3, -], in which case there is clearly no DMA race.

The program of Figure 6(b) is the same as that of Figure 6(a), except that the wait(t) operation has been removed. This results in a potential DMA race, since data may be simultaneously read from and written to l. The left- and right-hand-sides of Figure 8 illustrate the transition systems for this program when the explicit and implicit encodings are used, respectively. Comparing the right-hand-sides of Figures 7 and 8, observe the same nondeterministic choice to track get(l, h, s, t) is initially made. However, in Figure 8 the choice to track this operation is not invalidated by a subsequent wait operation, since no such operation occurs in the program of Figure 6(b). As a result, an attempt to execute operation put(l, h + s, s, t) can be made from the state [2, get(l, h, s, t)], leading to a DMA race.

## 5.4 Handling fences and barriers

As discussed in §2.1, DMA subsystems such as that of the Cell processor typically support modified versions of get and put that use *fences* and *barriers* [IBM09].

Recall from  $\S 2.1$  that a fenced put/get operation (denoted putf/getf) identified by tag t will not commence until all currently pending operations identified by tag t have completed. However, the fenced operation provides no guarantees for future operations on t. A put/get operation with barrier (denoted putb/getb) identified by tag t similarly will not commence until all currently pending operations identified by tag t have completed. In addition, future operations identified by tag t will not commence until operations pending before issue of the barrier have completed. However, a barrier does not protect itself from future operations identified by t.

Note that the operation  $\operatorname{putb/getb}(l,h,s,t)$  is *not* equivalent to the sequence  $\operatorname{wait}(t)$ ;  $\operatorname{put/get}(l,h,s,t)$ . In the latter case, the  $\operatorname{wait}(t)$  operation causes execution to block until the DMA operation on tag t has completed. In the former case, the DMA barrier is a non-blocking operation.

To extend our existing encodings to handle fences we weaken the DMA race check condition to allow a new DMA to overlap with an existing DMA if the new DMA is a fenced operation and both DMAs are identified by the same tag.

Adapting our encodings to support barriers requires an additional *protected* flag to be associated with each tracked DMA. For any DMA (including a barrier), *protected* is initially set to 0. When a barrier DMA is issued with identifying tag *t*, *protected* is set to *true* for every existing DMA identified by *t*. The DMA race check condition is then weakened (for all types of DMA, not just barriers) to permit a new DMA to overlap with an existing DMA if both DMAs are identified by the same tag and *protected* holds for the existing DMA.

In Figure 9, we show how the implicit encoding of Figure 5 can be extended with support for fence and barrier operations. The explicit encoding of Figure 4 is extended in a similar manner. In Figure 9, to avoid redundancy in our presentation of the translation for barrier operations, we write "translation for get/put(l,h,s,t)" to denote the statements obtained by applying the translation for get/put(l,h,s,t) verbatim.

Note that protected is set to 0 for all newly issued DMA operations, including barriers. This is because, as discussed above, a barrier identified by tag t protects all prior operations identified by t, but not itself, from future operations identified by t.

#### 6 k-Induction for goto programs

Our encodings of DMA programs are directly amenable to analysis via bounded model checking [BCC<sup>+</sup>03] as an effective method to discover DMA races. However, BMC alone cannot be used to verify the (unbounded) *absence* of DMA races in programs with loops.

The k-induction procedure [SSS00], proposed as a method to allow verification of hardware designs (represented as finite state machines) using a SAT solver, is a stronger version of the standard invariant approach to verify safety properties. Using normal invariants, proving that a system satisfies a safety property  $\phi$  requires showing that

- (i) some formula I (possibly identical to  $\phi$ ) holds in all initial states,

- (ii) I is preserved by all state transitions of the system (I is *inductive*), and

- (iii) I implies  $\phi$ .

The main difficulty of this method is the construction of inductive formulae I. The k-induction principle addresses this difficulty by weakening (ii) to the property that I has to be preserved only if it held in the previous k states of execution. In return, (i) has to be strengthened appropriately.

We describe the principle using the notation of [ES03]. Let  $\mathbf{I}(s)$  and  $\mathbf{T}(s,s')$  be formulae encoding the initial states and transition relation for a finite state system over sets of propositional state variables s and s', and  $\mathbf{P}(s)$  a formula representing states satisfying a safety property. For  $k \geq 0$ , to prove  $\mathbf{P}$  by k-induction it is required first to show that  $\mathbf{P}$  holds in all states reachable from an initial state within k steps, i.e. that the following formula (the base case) is unsatisfiable:

$$\mathbf{I}(s_1) \wedge \mathbf{T}(s_1, s_2) \wedge \cdots \wedge \mathbf{T}(s_{k-1}, s_k) \wedge (\overline{\mathbf{P}(s_1)} \vee \cdots \vee \overline{\mathbf{P}(s_k)})$$

.

Secondly, it is required to show that whenever  $\mathbf P$  holds in k consecutive states  $s_1,\ldots,s_k$ ,  $\mathbf P$  also holds in the next state  $s_{k+1}$  of the system. This is established by checking that the following formula (the step case) is unsatisfiable:

$$\mathbf{P}(s_1) \wedge \mathbf{T}(s_1, s_2) \wedge \cdots \wedge \mathbf{P}(s_k) \wedge \mathbf{T}(s_k, s_{k+1}) \wedge \overline{\mathbf{P}(s_{k+1})}$$

.

In principle, k-induction can be used for SAT-based software model checking "out-of-the-box". A program can be encoded as a monolithic transition function, where the program

counter is an explicit variable. Assertions appearing in the original program can be gathered together into a single invariant. The encoded program and invariant can be represented as a SAT formula, to which *k*-induction can be applied.

This naïve encoding has not shown success in practice due to the loss of structure associated with the translation process. Furthermore, an important refinement which boosted the applicability of k-induction to hardware designs is the restriction to loop-free paths [SSS00]. This refinement is not useful when dealing with software, where the state-vector is very large, leading to extremely long loop-free paths. To see this, consider a program consisting of a simple loop, which increments a counter until some statically unknown maximum value is reached:

```

void f (unsigned int x) {

unsigned int i;

i = 0;

while(i <= x) {

i++;

}

}</pre>

```

For a fixed word size d, the length of the longest loop-free path in the program's state-space exceeds  $2^d$ , the number of possible integer values for this word size. Because realistic programs involve many loops, frequently with unknown bounds, applying k-induction with a value of k as large as the longest loop-free path in the state space is not feasible.

To verify absence of DMA races in goto programs, we present a novel formulation of k-induction, which operates at the loop level, and prove its correctness (§6.1). We then give some intuition as to why k-induction is effective in proving absence of DMA races in example programs written for the Cell processor (§6.2); this intuition is backed up by experimental results in §7.

## 6.1 A proof rule for k-induction with loops

To present our proof rule for k-induction we require some additional machinery and notation. Given programs  $\alpha = 1$ :  $\alpha_1; \ldots; m$ :  $\alpha_m$  and  $\beta = 1$ :  $\beta_1; \ldots; n$ :  $\beta_n$ , the *size* of  $\alpha$ , denoted  $|\alpha|$ , is m, and we define the sequential composition of  $\alpha$  and  $\beta$  as follows:

```

\alpha \circ \beta =_{\mathsf{def}} 1: \alpha_1; \ldots; m: \alpha_m; m+1: \beta_1; \ldots; m+n: \beta_n.

```

For i > 0, we use  $\alpha^i$  to denote the sequential composition of i copies of  $\alpha$ , and  $\alpha^0$  to denote the empty program. For a single-statement program of the form 1:  $\alpha_1$ , we drop the leading 1:, writing simply  $\alpha_1$ .

**Definition 2** A program  $\alpha$  is *self-contained*, denoted  $contained(\alpha)$ , if, for each goto statement i: goto ..., l, ... appearing in  $\alpha$ , we have  $(i + l) \in \{1, ..., |\alpha| + 1\}$ .

In other words, goto statements can only change the instruction pointer to the locations of statements inside  $\alpha$ , or to the location immediately following  $\alpha$ . The traces of programs formed using concatenation of self-contained components can be derived from the traces of the components (this is formalized in Lemma 1 below).

In our version of k-induction, assertions contained in a program are used as invariants. To turn assertions into induction hypotheses in this setting, we define a function that replaces all assertions in a program with assumptions. Given a program  $\alpha=1:\alpha_1;\ldots;n:\alpha_n$ , the corresponding program  $\alpha_{assume}=1:\alpha_1';\ldots;n:\alpha_n'$  is defined by:  $\alpha_i'=\alpha_i$  assume  $\alpha_i'=\alpha_i$  otherwise.

Finally, we present *k*-induction as a proof rule operating on distinguished loops in a goto program of the following form:

$$\alpha$$

; goto  $1, (|\beta| + 2)$  ;  $\beta$  ; goto  $(-|\beta| - 1)$  ;  $\gamma$

where  $\alpha$ ,  $\beta$  and  $\gamma$  are self-contained. The program consists of a prelude  $\alpha$ , a loop with body  $\beta$  and a tail  $\gamma$ . Other than self-containedness, we do not make any assumptions about the shape of components  $\alpha$ ,  $\beta$  and  $\gamma$ , which may contain further (nested) loops and arbitrary control structure. We do not demand the presence of an explicit loop condition: loop condition b can be simulated by choosing assume b as the first statement of the loop body, and assume  $\neg b$  as the first statement of the tail. Note that the restriction to self-contained components is mild, e.g. early exit from the loop via a break statement can be simulated by a flag together with an appropriate loop condition. Our implementation of k-induction (see §7) can be applied to C programs with arbitrary loop structures, provided the control-flow-graph associated with a given program is reducible [ALSU06].

## Proof rule for k-induction

$$\begin{array}{c} contained(\alpha) & contained(\beta) & contained(\gamma) & k \geq 0 \\ \alpha \ ^{\circ} \ \gamma \ \text{is correct} & \{\alpha_{assume} \ ^{\circ} \ \beta^{i-1}_{assume} \ ^{\circ} \ \beta \ ^{\circ} \ \gamma \ \text{is correct} \}_{i \in \{1,...,k\}} \\ & \frac{\beta^{k}_{assume} \ ^{\circ} \ \beta \ \text{is correct}}{\alpha \ ^{\circ} \ \text{goto} \ 1, (|\beta|+2) \ ^{\circ} \ \beta \ ^{\circ} \ \text{goto} \ (-|\beta|-1) \ ^{\circ} \ \gamma \ \text{is correct}} \end{array}$$

In this rule, the assertions present in the program (e.g. the formulae in Figures 4, 5 and 9) take the role of the inductive invariant needed for verification. The premises include base cases requiring the program to be shown correct when the prelude, followed by between zero and k loop iterations, are executed. The premises  $\beta_{assume}^k$   $\beta$  is correct and  $\beta_{assume}^k$   $\beta$  is correct form the induction step, establishing that if it is possible to execute k loop iterations from an arbitrary state without violating any assertions then it is possible to successfully execute a further loop iteration, or the loop tail.

## **Theorem 1** (Correctness) The above proof rule is sound.

Before we can prove the correctness of Theorem 1, we need to characterize the traces of programs constructed by concatenation of self-contained programs. The next lemma follows directly from the trace semantics of goto programs (§4) and the definition of self-contained programs (Definition 2):

**Lemma 1** Suppose  $\alpha, \beta$  are self-contained programs such that  $|\alpha| = n$ . Given the state  $t = (\sigma, pc) \in S$ , we write  $t^n = (\sigma, pc + n)$  for the state with instruction pointer shifted by  $n \in \mathbb{Z}$  (with the special case  $\xi^n = \xi$ ). The traces of  $\alpha$  ;  $\beta$  are:

In the first case,  $t_1 t_2 \cdots$  denotes both finite and infinite traces of  $\beta$ , while  $s_1 s_2 \cdots$  in the last case is an infinite trace.

We also require the following simple result about the relationship between programs  $\alpha$  and  $\alpha_{assume}$ :

**Lemma 2** The traces of  $\alpha$  and  $\alpha_{assume}$  are related as follows:

$$traces(\alpha_{assume}) = \{s \in traces(\alpha) \mid s \text{ does not contain } \}$$

Proof (Theorem 1) With the help of Lem. 1, it can be observed that the program

$$\alpha$$

; goto  $1, (|\beta|+2)$  ;  $\beta$  ; goto  $(-|\beta|-1)$  ;  $\gamma$

$$\alpha_1 \, \, \stackrel{\circ}{,} \, \, \alpha_2 \, \, \text{is correct} \, \Rightarrow \, \alpha_1 \, \, \text{is correct}$$

(1)

$$\alpha_1$$

and  $\alpha_1_{assume} \ \ \alpha_2$  are correct  $\Rightarrow \alpha_1 \ \ \alpha_2$  is correct (2)

We have:

- $\alpha$  is correct: by (1), this follows from the correctness of  $\alpha \circ \gamma$ .

- $\alpha$ ;  $\beta^i$  is correct for  $i \in \{1, \ldots, k\}$ : this is proven by induction on i. We assume that  $\alpha$ ;  $\beta^i$  is correct (for  $i \in \{0, \ldots, k-1\}$ ) and show the correctness of  $\alpha$ ;  $\beta^{i+1} = \alpha$ ;  $\beta^i$ ;  $\beta$ . From the correctness of  $\alpha_{assume}$ ;  $\beta^i_{assume}$ ;  $\beta^i_{assume}$

- $\alpha$   $\S$   $\beta^i$  is correct for i > k: again, we reason by induction over i and assume that  $\alpha$   $\S$   $\beta^i$  is correct for some  $i \geq k$ . Because  $\beta^k_{assume}$   $\S$   $\beta$  is correct, so is  $\alpha_{assume}$   $\S$   $\beta^{i-k}_{assume}$   $\S$   $\beta^k_{assume}$   $\S$   $\beta$  (by Lem. 1), which together with (2) and the induction hypothesis entails the correctness of  $\alpha$   $\S$   $\beta^{i+1}$ .

- $\alpha$  ;  $\gamma$  is correct: given as premise of the rule.

- $\alpha$   $^{\circ}$   $\beta^{i}$   $^{\circ}$   $\gamma$  is correct for  $i \in \{1, \ldots, k\}$ : follows from the correctness of the programs  $\alpha_{assume}$   $^{\circ}$   $\beta^{i-1}_{assume}$   $^{\circ}$   $\beta$   $^{i}$   $\gamma$  and  $\alpha$   $^{\circ}$   $\beta^{i-1}$ , and (2).

By presenting k-induction using a general proof rule, we do not restrict the method to a SAT-based implementation. Although our practical implementation is SAT-based, the rule could also be used in any (possibly interactive) deductive verification system.

## 6.2 k-induction for DMA programs

Through our experiments in  $\S 7$  we observe that k-induction works extremely well for checking assertions representing DMA race-freeness, generated by the rules in Figures 4, 5 and 9. For realistic example programs written for the Cell processor, the generated assertions are mostly inductive already for small k, with no further annotations required to verify correctness. The result is a verification method that is fully automatic and efficient on a large range of Cell programs. For a small number of benchmarks we find that the implicit encoding of DMAs does not yield inductive assertions, while the explicit encoding does. We discuss this in detail in  $\S 7.5$ .

Intuitively, k-induction works well in this application domain because DMA operations in loops are typically designed to be pending for only a bounded number of loop iterations, allowing k-induction to succeed with a value of k proportional to the bound. This is analogous to the intuition that k-induction works well for sequential hardware circuits with pipelines, where the k required for induction to succeed is proportional to the pipeline depth [AFF<sup>+</sup>05].

## 7 Experimental evaluation

## 7.1 SCRATCH

We have implemented a prototype tool, SCRATCH<sup>4</sup>, built on top of the bounded model checker CBMC [CKL04]. SCRATCH accepts an arbitrary C program written for an SPE core of the Cell BE processor, and checks for DMA races involving scratch-pad memory. The tool uses the encodings described in §5 to transform the input program into a form where DMAs are replaced with assertions and assignments over tracker variables. In the case of the explicit encoding, the size *D* of the tracker arrays is specified as a command-line argument to SCRATCH.

Having translated the input program into an instrumented form, SCRATCH can apply bounded model checking to check for DMA races up to a certain execution depth. To prove absence of races, SCRATCH combines bounded model checking with k-induction, using the loop-level formulation of §6. For a program consisting of a single, non-nested loop (with prelude and tail), k-induction is applied starting with k=0, and incrementing k by one until either the base case fails (a DMA race has been detected), both the base case and step case succeed (the program has been proved free of DMA races), or k exceeds 10. The starting value, step size and upper limit for k can be configured via command-line arguments. For such restricted loops, the combination of k-induction and SAT-based bounded model checking is sound: the base and step case programs generated by the k-induction proof rule are loop-free, thus SAT-based bounded model checking can provide an exhaustive analysis.

Handling multiple loops. SCRATCH can be applied to arbitrary sequences of loop nests (as long as the control-flow-graph associated with the input program is reducible [ALSU06]). A sequence of loop nests is automatically transformed into a single, monolithic loop simulating the nest, using the following well-known technique [Har80]. A position variable is used to record which of the original loop bodies is due to be executed. The body of the monolithic loop consists of a case-split on this variable, where each case contains the body of the corresponding loop, together with code to update the position variable appropriately. Once this transformation has been applied, k-induction can be used to directly analyze the monolithic loop, since unwinding this loop leads to a loop-free program.

We also experimented with handling sequences of loop nests by applying the k-induction rule recursively as follows. Given a sequence of loop nests, k-induction is applied to the first outer loop. Unwinding this loop to yield a base case and step case results in programs which themselves contain loops. The k-induction rule can then be applied again to each of these programs, in an attempt to prove their correctness by induction. This process leads to a tree of programs to be analyzed: an interior node n of this tree is a program containing loops;

<sup>&</sup>lt;sup>4</sup> SCRATCH, together with source code for all benchmarks, is available online: http://www.cprover.org/scratch/.

the left and right children of n are the base and step cases associated with a  $k_n$ -inductive proof of correctness for n. (Note that the values  $k_n$  used for separate inductive proofs are independent.) The leaf nodes of the tree are loop-free programs which can be analyzed using SAT-based bounded model checking.

We have implemented both of the above approaches. In the absence of heuristics for guessing effective starting and increment values for k, the transformation to a monolithic loop leads to faster verification of our benchmark examples. This transformation is used in our experimental evaluation.

## 7.2 Benchmarks and experimental platform

We evaluate SCRATCH using a set of 22 benchmarks adapted from examples supplied with the IBM Cell SDK for Multicore Acceleration [IBM09], categorized as follows:

- x-buf ( $x \in \{1, 2, 3\}$ ) Eleven data processing programs which use single-, double- or triple-buffering for data-movement (cf. Figure 2). 'I/O' in the benchmark title indicates that separate buffers are used for input and output. Some variants of these programs use fences/barriers, indicated by '+ fence'/'+ barrier' in the benchmark title

- race check, simple dma Examples which illustrate data races and use of DMA

- sync atomic/mutex Programs illustrating the use of SDK synchronization primitives for atomic operations and mutexes, in conjunction with DMA operations

- cpaudio, normalize Applications which copy one channel of a stereo audio file to the

other, and normalize the volume of a mono audio file, respectively

- checksum Computes a checksum on data in host memory. Multiple buffers are used to coordinate data-movement efficiently

- Euler simple/complex Particle simulation using Euler integration. The simple version uses separate individual buffers for position, velocity and mass data; the complex version uses double-buffering

- Julia n Quaternion Julia set ray-tracing, where an SPE renders n columns of output

As discussed in §3, manual program slicing has been applied to each benchmark to remove portions of code that do not affect DMA operations. This routine slicing could be automated: the sliced code uses vector datatypes and intrinsic functions specific to the Cell processor, which the slicer would need to understand. After slicing, most of the benchmark examples consist of a single, non-nested loop. The *Euler simple, Euler complex* and *Julia* benchmarks each involve a loop containing a nested inner loop.

We apply SCRATCH to correct and buggy versions of the benchmarks. With the exception of 3-buf and cpaudio, bugs are injected into the examples, either by removing a wait operation, changing the tag used to identify a DMA, or switching an operation from get to put (or vice-versa). The 3-buf benchmark is the triple-buffering example discussed in §2.3, in which SCRATCH uncovered an existing bug. A DMA race occurs when the cpaudio benchmark is executed with zero frames of audio. This is arguably a bug since the precondition that the number of frames should be positive is not specified.

We present results demonstrating the effectiveness of SCRATCH, equipped with either the explicit or implicit encoding of  $\S 5$ , for bug-finding and proving correctness with respect to DMA races. Experiments are performed on a 3GHz Intel Xeon quad-core machine with 48 GB RAM, running Ubuntu. MiniSat 2.0, compiled with full optimizations, is used as a back-end SAT solver. It has been reported to perform comparatively to state-of-the-art SMT solvers for SMT- $\mathcal{BV}$  [CFMS09] on this type of workload. All times reported are averaged over 5 consecutive runs.

## 7.3 Bug-finding

With both encodings, bounded model checking proves extremely effective for detecting DMA races. For each benchmark and each encoding, we performed repeated bounded model checking runs to find the minimum execution depth required to exhibit a DMA race. For the explicit encoding, we also iteratively computed, for each benchmark, the smallest value of D (the size of the tracker arrays) necessary to allow race detection. We then measured the time taken for verification (instrumentation + bounded model checking) using these minimum values, averaged over multiple runs.

With the explicit encoding, the maximum verification time across all benchmarks is 1.32s; this is for one of the *race check* examples. For each benchmark, time taken for verification with the implicit encoding is identical or marginally lower, with a maximum time of 0.87s for the same *race check* example. This gap of 0.45s is the largest difference between the two encodings exhibited for our benchmarks with respect to bug-finding—a speedup of  $1.52\times$  using the implicit encoding instead of the explicit encoding. The bugs in our benchmarks are relatively shallow; all bugs are found within an execution depth of 523 and 320 statements in the C program for the explicit and implicit encodings, respectively.

By reporting verification times for the explicit encoding when the optimal value of D is used, we have shown the explicit encoding in a favorable light. When using the explicit encoding in practice, one would have to guess a suitable value for D. Guessing a larger value than necessary would result in large BMC instances, while guessing too small a value would result in failed verification attempts. The implicit encoding does not suffer from this practical constraint.

## 7.4 Proving correctness.

Figure 10 presents experimental data obtained applying SCRATCH to correct versions of the benchmarks, using both the explicit and implicit encodings. For each encoding, the time (in seconds) taken for verification is shown, together with the smallest value of k required to prove correctness. Assuming that the required k is m (for some  $m \geq 0$ ), verification time is the sum of the times for program instrumentation, construction of base/step case programs for  $0 \leq k \leq m$ , successful bounded model checking of step case programs for  $0 \leq k < m$ , and successful bounded model checking of the final step case program for k = m.

As with the results for bug-finding, we iteratively computed the smallest value of D required to prove correctness using the explicit encoding, and report results for the explicit encoding when optimum values for D are used; the optimum value for D is shown, for each benchmark, in Figure 10. Again, this shows the explicit encoding in a favorable light: in practice one would have to guess a suitable value for D; this is not necessary when the implicit encoding is used.

Figure 10 also shows the size (number of variables and number of clauses) of the largest SAT instance solved for each benchmark during k-induction. In all cases, this corresponds to the SAT instance associated with verification of the final step-case program.

In five cases, we found that DMA race freedom could be proved automatically using k-induction, for a small value of k, with the explicit encoding but *not* with the implicit encoding. This scenario is indicated by '-' entries in Figure 10, and indicates that k-induction did not succeed for  $k \le 10$ . We discuss reasons for this in detail in §7.5. In each case, it is possible to manually add a simple strengthening assertion to allow k-induction to succeed

with the implicit encoding; we give an example of this in §7.5. In Figure 10, rows marked 'strengthened' show results for variants of benchmarks with strengthening assertions.

When k-induction succeeds for both encodings, the values of k required are identical, or differ by one due to benchmark-specific differences in the strength of the induction hypothesis yielded by assertions associated with each encoding.

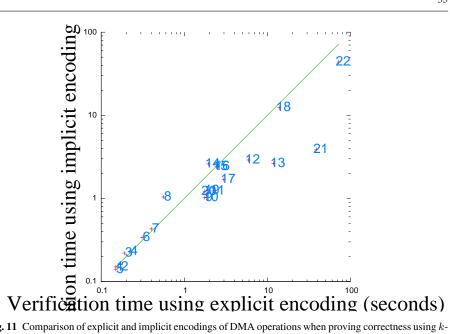

The results of Figure 10 indicate that k-induction provides a tractable method for proving correctness for this set of benchmarks: for both encodings (excepting cases where kinduction does not succeed for the implicit encoding), the maximum time taken for verification is less than 73 seconds. Restricting our attention to benchmarks where k-induction succeeds for both encodings (17 of the standard benchmarks, plus 5 strengthened benchmarks), we see that the implicit encoding outperforms the explicit encoding in the majority of cases. This is highlighted by the scatter plot of Figure 11, which plots (using a logarithmic scale) the relationship between verification times with both encodings for each benchmark; benchmarks are identified by their row number in Figure 10. In some cases, the implicit encoding significantly outperforms the explicit encoding: verification with the implicit encoding is 10 times faster for the Euler complex benchmark. This is due to the dependence of the explicit encoding on D, the maximum number of operations that may be simultaneously pending. For the Euler complex benchmark, D is relatively large, which necessitates the solving of large SAT instances, as shown in Figure 10. By comparison, the largest SAT instance associated with the implicit encoding for this benchmark is almost ten times smaller, since the implicit encoding is independent of the parameter D.

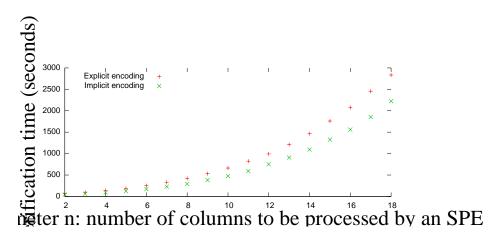

The *Julia* benchmark contains a loop for which the number of iterations is a fixed parameter n, the columns of a raytraced image to be computed by one SPE. For this example, k-induction succeeds with k=n+6 for the explicit encoding, and k=n+5 for the implicit encoding. The results in Figure 10 are for the case where n=2. In Figure 12, we illustrate the scalability of k-induction by plotting the time taken for verification of the Julia benchmark when we vary parameter n between 2 and 18. Growth is less than cubic, showing that our k-induction method scales well.

### 7.5 Examples where the implicit encoding is too weak for k-induction

As mentioned above, and as indicated in Figure 10, our benchmarks reveal examples where k-induction succeeds with the explicit encoding of DMA operations, but not with the implicit encoding. We discuss the reasons for this by considering one of the examples, the *checksum* benchmark, in detail.

The *checksum* benchmark uses four local buffers, numbered 0, 1, 2 and 3, to receive data from host memory via DMA. Each buffer has size  $2^{12}$  bytes, and the collection of four buffers is implemented as a  $4\times 2^{12}$  array of type **char**, called buf. At the start of the program, the value  $2^{12}$  is written to a variable, size. There follows a data processing loop with induction variable i such that, on iteration i ( $i=0,1,\ldots$ ), a get operation is issued to copy  $2^{12}$  bytes of data from host memory into buffer i%4, i.e. into the region  $[(i\%4)\times 2^{12},(i\%4+1)\times 2^{12})$  of buf. However, the variable size, rather than the explicit constant  $2^{12}$ , is specified as the size argument to the get command. The loop is structured so that DMA operations targeting all four buffers may be simultaneously pending.

When proving the step case for k-induction, the value of size is havocked: the model checker considers paths from the start of the loop from states where size is arbitrary. In particular, states where size is larger than  $2^{12}$  are considered. Such states can clearly lead to DMA races, e.g. a get operation requesting that more than  $2^{12}$  bytes are transferred into

buffer 0 will result in buffer overflow: the get operation will target memory locations that form part of buffer 1. This will lead to a DMA race during the next loop iteration, when a get is issued targeting buffer 1. Such states are, of course, unreachable, since size is set to  $2^{12}$  before the loop and is never modified further. The assertion  $size \leq 2^{12}$  is part of the invariant required to show correctness of the program.

With the explicit encoding, this assertion is computed indirectly via k-induction. A history of four DMA operations is tracked (D=4). Thus, when proving the step case for k=4 the model checker assumes that, on loop iteration  $i\geq 4$ , the DMA operations issued in previous loop iterations did not race. This assumption is clearly false in states where size is greater than  $2^{12}$ , thus states which do not satisfy the invariant  $size \leq 2^{12}$  are not considered by the model checker as initial states when checking the step case.

With the implicit encoding, increasing k does not yield this invariant. This is because the implicit encoding tracks a single, arbitrary DMA operation. Consider a state where  $size=2^{12}+1$  and i%4 = 3. Executing four iterations of the loop results in get operations targeting buffers 3, 0, 1 and 2, in that order. Call these operations  $get_3$ ,  $get_0$ ,  $get_1$  and  $get_2$ . Since  $size=2^{12}+1$ , operation  $get_j$  targets the region  $r_j=[j\times2^{12},(j+1)\times2^{12}]$  of buf. Consider a trace where  $get_3$  is nondeterministically chosen for tracking. When  $get_0$ ,  $get_1$  and  $get_2$  are issued, they are checked with respect to  $get_3$ . No race is detected for  $get_0$  and  $get_1$ , since  $r_3\cap r_0=\emptyset$  and  $r_3\cap r_1=\emptyset$ . However,  $r_3\cap r_2=\{3\times2^{12}\}$ , thus there is a DMA race between  $get_3$  and  $get_2$ . For any k, we can construct a path consisting of k loop iterations, ending in a state where  $size=2^{12}+1$  and i%4=3, along which no DMA is tracked. We can correctly assume that no DMA race is detected along such a path. However, as demonstrated above, the path can be extended so that a DMA race occurs. Thus, for any k, we have a counterexample to k-induction.

The essential point here is that with the explicit encoding, the combination of multiple DMA operations yields the invariant  $size \leq 2^{12}$ , whereas the implicit encoding considers operations in isolation, and does not derive this invariant.

The implicit encoding with k-induction fails on four further benchmarks, as indicated in Figure 10, for similar reasons. In all cases, the induction hypothesis can be strengthened so that k-induction succeeds for the implicit encoding, by adding a simple assertion to the body of the loop. For example, for the *checksum* benchmark, adding assert  $size = 2^{12}$  to the loop body suffices. Experimental results for strengthened benchmarks are presented in rows marked 'strengthened' in Figure 10.

## 7.6 Comparison with predicate abstraction

The translation implemented by SCRATCH operates at the level of control flow graphs. In order to compare with other tools, we have hand-translated three of our benchmarks, *1-buf*, *2-buf* and *3-buf*, into C programs that track DMA operations as described in §5. We aimed to compare with BLAST [BHJM07] and SATABS [CKSY05] but were unable to obtain results using BLAST due to a bug in the tool, which we have reported to the BLAST developers.

Figure 13 shows results for proving correctness and finding bugs using SATABS (version 2.5), with Cadence SMV as a back-end model checker. For each example, we show the number of refinement iterations required (*iterations*), the time taken for verification (*time*), and the speed-up factor obtained by using SCRATCH over SATABS (obtained by comparing with the results of Figure 10). The explicit encoding is used in all cases. For buggy versions of *1-buf* and *2-buf*, SATABS is able to find the bug within 100 iterations, but is two orders of magnitude slower than SCRATCH when applied to *2-buf*. The abstraction-refinement process

leads to a conclusive verification result when applied to the correct version of 1-buf, but is almost five times slower than our k-induction technique. SATABS was not able to find the bug in the buggy version of 3-buf, or prove correctness of correct versions of 2-buf or 3-buf within 100 refinement iterations.

## 7.7 Comparison with IBM Race Check library

The IBM Cell SDK [IBM09] comes with a library for detecting DMA races [IBM08] at runtime. The library maintains a log of pending operations, checking each new operation against entries in the log in a manner similar to our explicit encoding. If a DMA race is detected, then an error message is written to the console.

Using a Sony PlayStation 3 console, which is equipped with a Cell processor, we tested the Race Check library on each of our buggy examples. DMA races are detected for all but two benchmarks, and race detection takes less than  $0.1\,s$  in each case. The bug in *cpaudio* was not detected since the example runs on a specific input file that does not expose the bug. Although the buggy version of *1-buf I/O* crashes when executed on the Cell hardware, the Race Check library does not detect the DMA race responsible for this crash. This false negative appears to be a bug in the Race Check library rather than a fundamental limitation, since *1-buf I/O* is similar to examples where the Race Check library successfully detects DMA races.

Note that runtime race detection cannot be used to prove *absence* of DMA races, unlike our *k*-induction method.

## 8 Related work

The concept of *k*-induction was first published in [SSS00,BC00], targeting the verification of hardware designs represented by transition relations (although the basic idea had already been used in earlier implementations [LS99] and a version of one-induction used for BDD-based model checking [DM97]). A major emphasis of these two papers is on the restriction to loop-free or shortest paths, which we do not consider in our *k*-induction rule due to the size of state vectors and the high degree of determinism in software programs. Several optimizations and extensions to the technique have been proposed, including property strengthening to reduce induction depth [VH07], improving performance via incremental SAT solving [ES03], and supporting verification of temporal properties [AFF<sup>+</sup>05]. Applications of *k*-induction have focused exclusively on hardware designs [SSS00,BC00,LS99], synchronous programs [HT08,Fra06] and, recently, SystemC designs [GLD10]. A principle related to *k*-induction has also been used for circular reasoning about liveness properties [McM99].

To the best of our knowledge, there has been no previous work on applying k-induction to imperative programs comparable to our procedure in  $\S 6$ . Our formulation of k-induction, and the explicit encoding of DMA operations, were first presented in [DKR10]. A technique for strengthening k-induction in the context of DMA race analysis, using static analysis techniques, has been proposed [DHK11]; this work sketches the implicit encoding of DMA operations presented in full in this paper. As discussed in  $\S 7.5$ , the implicit encoding of DMA operations may lead to assertions that are not k-inductive, where the explicit encoding would yield k-inductive assertions. The strengthening techniques of [DHK11] can be used

to overcome this weakness of the implicit encoding, automatically inferring the kinds of strengthening assertions discussed in §7.5. The SCRATCH tool is also described in [DKR11].